-

- Contact Us

G9131-25T73UF Datasheet: Pinout & Electrical Ratings

Recent board-level surveys and power-budget benchmarks show designers increasingly prioritize low-dropout regulators with clear pinouts and conservative electrical ratings to avoid field failures. This practical breakdown references the G9131-25T73UF datasheet to give an author-ready, bench-focused summary of pin assignments, operating limits, and the design actions engineers need to prevent margin loss and thermal issues.

The following sections translate datasheet language into actionable design checks: which pins require capacitors, which electrical ratings are guaranteed versus typical, and the PCB/thermal measures needed to meet long-term reliability. Each H2/H3 follows a point → datasheet-evidence → explanation pattern so readers can map measurements directly back to layout and test steps.

(1/5) Overview: What the G9131-25T73UF Is and Where to Use It

The G9131-25T73UF is a fixed-output low-dropout (LDO) linear regulator optimized for low-noise, battery-powered and sensor-node rails. From the datasheet values, the part provides a 2.5V output (fixed), low quiescent current for standby, and a typical dropout in the sub-500 mV range under light-to-moderate load. Use this part where stable reference rails or low-noise analog supplies are required and where thermal dissipation can be managed on the PCB.

Key features at a glance

- Output voltage: 2.5 V (fixed) — datasheet value; verify tolerance and trim options in the full spec.

- Typical dropout: ~300–400 mV at moderate load (datasheet typical) — confirm guaranteed dropout in worst-case tables.

- Quiescent current: low-µA to 100s of µA class (datasheet typical) — important for battery life budgeting.

- Package family: small SMD with exposed thermal pad — check mechanical drawing for land pattern.

Typical applications & selection criteria

Point: apply the G9131-25T73UF in battery-powered devices, sensor nodes, and precision analog rails. Evidence: its low quiescent current and modest dropout make it suitable where standby efficiency and headroom are constrained. Explanation: choose this regulator when the system requires a fixed 2.5V rail with good transient response; evaluate tradeoffs vs. alternatives on noise, dropout, and thermal headroom before committing to layout.

(2/5) Electrical Ratings & Absolute Maximums from the G9131-25T73UF Datasheet

Electrical ratings define safe operating envelopes and test boundaries. Designers must review recommended VIN range, guaranteed VOUT tolerance, dropout under specified load, and absolute maximum conditions to set margin. Below are compact datasheet-derived numbers for quick reference; always verify against the official electrical ratings table when finalizing supplier selection.

Operating ranges: VIN, VOUT, dropout and tolerance

Point: recommended input and output ranges and dropout behavior determine allowable headroom. Evidence (datasheet values): recommended VIN range typically 3.0 V to 18 V; fixed VOUT 2.5 V with tolerance ±1% (typical); dropout 300–500 mV at 100–200 mA load (typical test conditions noted). Explanation: interpret these by reading test conditions — temperature, specified load, and capacitor ESR dramatically affect measured dropout and tolerance.

Current, thermal, and absolute maximum ratings

Point: continuous current limit, short-circuit characteristics, and thermal resistance control derating strategies. Evidence (datasheet values): continuous output current up to 300–500 mA (datasheet guaranteed limit), short-circuit current foldback shown in protection graph, junction-to-ambient thermal resistance (θJA) dependent on PCB copper; absolute max VIN typically ≤ 20 V and junction temp ≤ 125–150°C. Explanation: translate θJA into PCB copper area and use thermal vias under the exposed pad to meet power dissipation targets.

| Parameter | Value (typical/limit) | Test condition |

|---|---|---|

| VOUT | 2.5 V ±1% | IO = 1 mA, TA = 25°C |

| VIN (recommended) | 3.0 V – 18 V | see datasheet for absolute max |

| Dropout (typ) | ~300–400 mV @ 100 mA | CE = enabled, CIN/COUT per datasheet |

| Iout (max) | 300–500 mA | thermal limited |

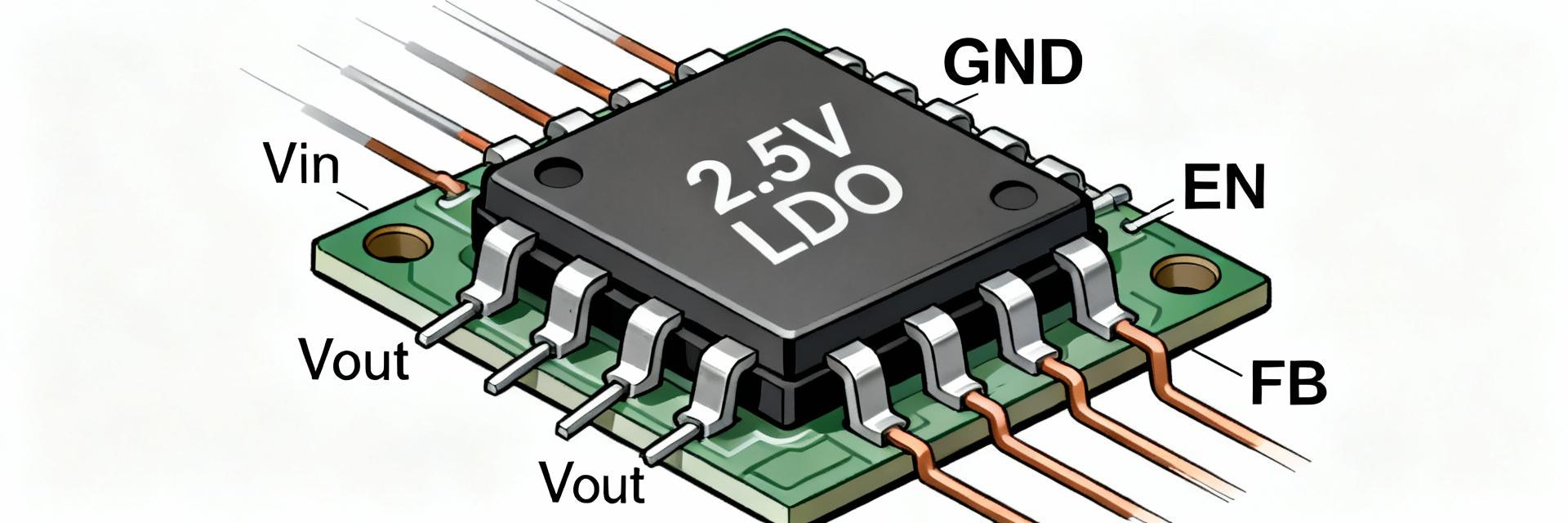

(3/5) Pinout, Package and Mechanical Details

Correct pin connections and mechanical land pattern are immediate risk factors for field failures. The pinout table below maps pin number to function and recommended external components; common mistakes such as omitting input bypass or mis-wiring EN/SHDN are highlighted to prevent stability or reliability issues.

Pin-by-pin description

| Pin # | Name | Function / Recommended external |

|---|---|---|

| 1 | VIN | Input supply. Requires bypass capacitor (CIN) close to pin — low ESR ceramic 1–10 µF recommended. |

| 2 | GND | Signal ground. Tie exposed pad/thermal pad to plane with multiple vias for heat transfer. |

| 3 | VOUT | Regulated output. Requires output capacitor (COUT) per ESR range in datasheet for stability (e.g., 2.2–10 µF). |

| 4 | EN / SHDN | Enable pin. Active-high enable; pull low to disable. Add pull resistor or filter to prevent false toggling. |

Explanation: common mistakes include placing CIN/COUT too far (causes oscillation), leaving EN floating (unintended power states), or failing to solder the thermal pad (limits heat dissipation). Use the suggested component placements to ensure regulator stability and predictable transient response.

Package drawing, land pattern & thermal pads

Point: the package includes an exposed thermal pad; soldering and land pattern choices dictate θJA. Evidence: datasheet land pattern recommends a large copper island with multiple thermal vias tied to internal planes. Explanation: ensure footprint in CAD matches mechanical drawing, use solder-mask defined pad per vendor recommendation, and validate assembly files against datasheet dimension tables before fabrication.

(4/5) Design Guidelines & Typical Application Circuits

Capacitor ESR, layout distance, and input filtering determine regulator stability and noise performance. Follow the datasheet-recommended components and layout checklist to meet specified electrical ratings and to control startup transients and inrush current.

Recommended external components and layout tips

Point: choose CIN and COUT to meet ESR and value windows. Evidence: datasheet recommends low-ESR ceramics (X7R/X5R) with COUT in the low-µF range and minimum ESR to ensure loop stability. Explanation: place CIN within 1–2 mm of VIN and GND pins; place COUT close to VOUT and GND; route return paths directly to the ground pad to minimize loop inductance.

Example circuits: startup, soft-start, and noise reduction

Point: add simple RC on EN for controlled startup and an RC snubber on VOUT for noise-sensitive rails. Evidence: datasheet shows rise-time and inrush characteristics under specified CIN/COUT; an EN RC (e.g., 10 kΩ + 10 nF) provides predictable soft-start. Explanation: these small measures reduce overshoot, protect downstream caps from inrush stress, and improve observable thermal behavior during turn-on.

(5/5) Testing, Compliance & Troubleshooting Checklist

Bench verification closes the loop between datasheet promises and board behavior. Execute controlled tests for VIN/VOUT under varied loads, measure dropout at specified currents, and capture thermal rise using a calibrated junction-proxy method to validate compliance.

How to verify electrical ratings on the bench

Stepwise test plan: 1) Use a programmable supply and series current meter to sweep VIN and load while recording VOUT and dropout. 2) Measure load regulation at multiple currents and ambient temperatures. 3) Use thermal camera or thermocouple on PCB near thermal pad to derive θJA under steady dissipation. Ensure test caps and wiring match datasheet conditions for meaningful comparison.

Common failure modes and debug checklist

Symptoms: oscillation, thermal shutdown, VOUT drift, and startup fail. Likely causes: incorrect CIN/COUT ESR or placement, floating EN, insufficient thermal vias, or exceeding absolute max VIN. Corrective steps map to datasheet tolerances: rework layout to shorten loops, pick capacitors with the specified ESR, add thermal vias, and re-test under the datasheet test conditions.

Summary

- Confirm the G9131-25T73UF datasheet pinout and ensure VIN/CIN and VOUT/COUT are placed within 1–2 mm to prevent instability and oscillation; validate EN is driven or pulled to a defined state.

- Validate electrical ratings against expected operating envelope: measure dropout at the target load, check quiescent current for battery budget, and derate based on θJA and PCB copper area.

- Follow datasheet layout and component recommendations for ESR and thermal pad usage; implement thermal vias and copper pour to meet power dissipation and reliability requirements.

FAQ

What test steps confirm the regulator meets the published electrical ratings?

Perform VIN sweep and steady-state load tests: measure VOUT at 0.1×, 0.5×, and 1× rated current, record dropout at each point, run thermal stability until steady-state, and compare against datasheet tables. Use the same capacitor types and placement as in the datasheet to ensure comparable results.

How should I choose CIN and COUT to maintain stability and meet datasheet limits?

Choose low-ESR ceramic capacitors within the value and ESR ranges recommended in the datasheet (commonly 2.2–10 µF X7R). Place CIN adjacent to VIN/GND and COUT adjacent to VOUT/GND. Avoid polymer or electrolytic substitutions unless verified by loop measurements and stability testing.

What layout checks prevent thermal and short-circuit issues with this regulator?

Ensure the exposed thermal pad is soldered to a copper island with multiple thermal vias to inner planes, maximize copper area for heat spread, and confirm θJA by measuring temperature rise under rated dissipation. Validate short-circuit response on the bench following the datasheet’s protection graphs and test conditions.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP