-

- Contact Us

MF-RX012 Performance Report: Key Specs & Datasheet

Introduction (data-driven hook)

Engineers expect polymeric PTC resettable fuses to exhibit predictable hold vs. trip currents, defined voltage ratings, and characteristic time‑to‑trip curves that span milliseconds to minutes depending on overload magnitude. This report distills the device’s critical electrical, thermal and application data from the official datasheet and test reports so design teams can accelerate selection and verification; the presentation highlights clear specs and datasheet cross‑references for rapid review. (Keyword: MF-RX012)

1 — Product background & overview (background introduction)

What MF-RX012 is and form factor

Point: The part is a polymeric positive temperature coefficient (PTC) resettable fuse in a radial through‑hole package. Evidence: Datasheet mechanical drawings and part‑number suffix notes identify the family as a polymer PTC with radial leads (see datasheet mechanical table). Explanation: This form factor is optimized for low‑voltage board‑level protection where simple through‑hole soldering and straightforward replacement are acceptable; designers should compare the listed specs against rail voltage and expected fault energy before selection.

Variant breakdown & part-number mapping

Point: Multiple current and voltage variants exist within the family, typically indicated by numerical suffixes and packaging codes. Evidence: The datasheet shows variant rows mapping hold/trip currents, voltage ratings and packaging notes (see datasheet table X for variant mapping). Explanation: Create a one‑line mapping from each part number to the datasheet row before procurement so procurement and test teams read the exact specs for the chosen variant.

2 — Key electrical specs at a glance (data analysis)

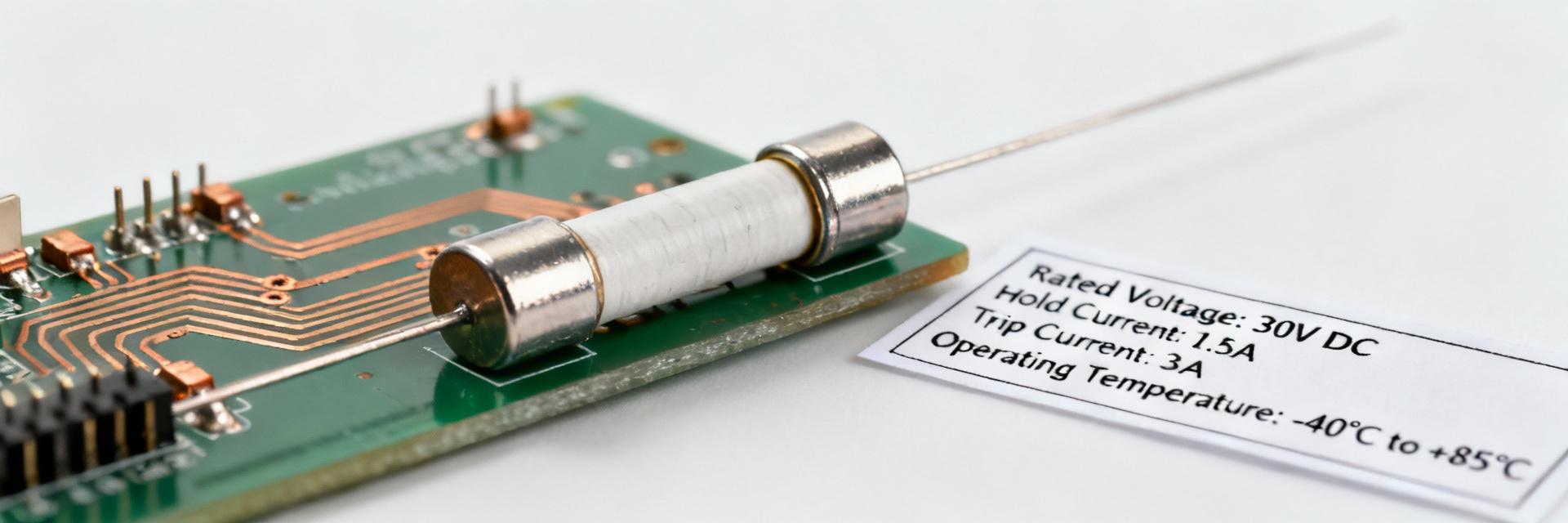

Hold current, trip current, and tolerated surge

Point: Designers must verify Ihold (maximum current device will maintain indefinitely) and It / Itrip (current at which the device trips within specified time). Evidence: The datasheet provides Ihold and Itrip per variant and time‑to‑trip ranges (see datasheet table Y). Explanation: Cross‑reference the selected variant’s Ihold/It values with expected operating and inrush currents; use the table below to compactly compare candidate variants against system currents before prototyping.

| Part Variant | Rated Voltage (V) | Ihold (A) | Itrip (A) | Note (datasheet row) |

|---|---|---|---|---|

| Variant A (example) | — (see table) | — (see table) | — (see table) | datasheet table Y, row 1 |

| Variant B (example) | — (see table) | — (see table) | — (see table) | datasheet table Y, row 2 |

Voltage rating, resistance & leakage

Point: Confirm maximum working voltage, initial DC resistance and any post‑trip leakage behavior. Evidence: The datasheet lists maximum working voltage and typical cold resistance per variant (see datasheet electrical table). Explanation: Use rated voltage to determine isolation and placement; compare initial resistance to power‑budget and measure after trip if the datasheet provides post‑trip resistance or leakage limits to ensure downstream circuitry remains safe during a trip event.

3 — Thermal & environmental specifications (data analysis / method guide)

Operating and storage temperature, max surface temp

Point: Temperature ranges and maximum surface temperature in the tripped state determine placement and clearance. Evidence: The datasheet gives operating/storage limits and maximum temperature rise or surface temperature in a tripped condition (see datasheet thermal table). Explanation: Maintain clearance from heat‑sensitive components and apply derating where ambient or internal heat sources push the device toward its maximum surface temperature during repeated trips.

Soldering, mounting, and reliability considerations

Point: Soldering profiles, lead heating limits and mounting recommendations affect long‑term reliability. Evidence: Mechanical and soldering notes in the datasheet specify peak lead temperatures and recommended through‑hole soldering practices (see datasheet mechanical notes). Explanation: Follow the datasheet’s soldering cautions; use standoff clearance to mitigate PCB heat soak and to enable consistent trip behavior over the product lifetime.

4 — Performance benchmarks & test data (data analysis / method guide)

Time‑to‑trip curves & time‑current characteristics

Point: Time‑current curves illustrate how long the device will hold at a given overcurrent. Evidence: The datasheet provides time‑vs‑current graphs (see datasheet figure Z). Explanation: Annotate the time‑current curve for common fault scenarios—slow overloads (e.g., sustained 1.5× Ihold) versus hard shorts (e.g., >5× Ihold)—to select variants that balance nuisance trips and protection.

Lifetime, cycle behaviour and derating

Point: Endurance and cycling behavior determine suitable derating. Evidence: The datasheet includes cycle test summaries and recommended derating guidance (see datasheet reliability section). Explanation: If the datasheet shows a decline in performance after repetitive surge cycles, apply conservative derating for continuous or repeated surge environments and plan for periodic verification in long‑life deployments.

5 — Application examples & circuit integration (case showcase)

Typical use cases and design examples

Point: The device suits telecom/data‑line and low‑voltage power rail protection. Evidence: Datasheet application notes and typical circuit sketches indicate recommended variants per use case (see datasheet application figure). Explanation: Example 1 — use a lower Ihold variant for data‑line protection to detect small overcurrents; Example 2 — select a higher Ihold variant for 5 V power rails where inrush is expected. These callouts help speed variant choice during schematic design.

- Telecom/data‑line protection — choose a sensitive variant to protect downstream line drivers while tolerating nominal line currents.

- Low‑voltage power rail — pick a variant with higher Ihold to survive inrush but trip on sustained faults.

- Battery‑powered modules — balance Ihold with minimal series resistance to preserve efficiency.

PCB footprint, layout and testing tips

Point: Lead spacing, thermal separation and test access affect both trip behavior and verification. Evidence: Mechanical drawing and thermal notes in the datasheet specify recommended clearances (see datasheet mechanical drawing). Explanation: Maintain recommended lead spacing, add a thermal keepout for nearby ICs, and include solder fillet controls; plan bench tests (measured Ihold and time‑to‑trip using controlled current ramps) to validate behavior on the actual PCB.

6 — Datasheet reading checklist & procurement verification (actionable checklist)

How to read and cross-check the datasheet quickly

Point: A concise checklist prevents missed mismatches between part choice and system needs. Evidence: Cross‑reference the electrical, thermal, mechanical and packaging tables in the datasheet (see datasheet table index). Explanation: Verify rated voltage, Ihold/Itrip, time‑current curves, max surface temp, soldering limits and mechanical footprint in order before approving a part for production.

- Confirm variant row in electrical table (Ihold, Itrip). — datasheet table Y

- Review time‑current curves for expected fault types. — datasheet figure Z

- Check maximum working voltage and insulation requirements. — datasheet electrical table

- Validate mechanical footprint and soldering notes. — datasheet mechanical drawing

- Inspect packaging and storage notes for long‑term reliability. — datasheet packaging notes

Incoming inspection & test protocol for buyers

Point: Minimal lab tests confirm lot conformity. Evidence: Datasheet test methods and acceptance criteria summarize expected electrical parameters (see datasheet test section). Explanation: Sample 10 pieces per lot, measure cold DC resistance, perform a controlled ramp to confirm Ihold and time‑to‑trip, and visually inspect for plating/lead integrity; reject if resistance exceeds datasheet tolerance or if trip behavior deviates from specified curves.

Key summary

- Confirm electrical ratings (Ihold/It and rated voltage) against system currents and inrush—use datasheet electrical tables as the authoritative source.

- Verify thermal and environmental limits, including maximum surface temperature and soldering constraints, to avoid heat‑related derating or nuisance trips.

- Validate time‑current behavior with bench ramps against the datasheet curves to ensure the chosen variant meets protection timing for target faults.

Common questions and answers

How to interpret the datasheet time‑current curve for MF-RX012?

Read the curve by locating the x‑axis (time) and y‑axis (current expressed as multiples of Ihold). The datasheet curve shows typical trip times for given overcurrents — designers should match expected fault currents to the curve and allow margin for component tolerances and board thermal conditions.

What specs from the datasheet are most critical for PCB placement?

Critical specs are maximum surface temperature in the tripped state, soldering/lead temperature limits, and mechanical footprint. Use these datasheet fields to set clearances and thermal keepouts so nearby components avoid heat stress during trips.

What minimal incoming tests confirm lot quality versus the datasheet?

Measure cold DC resistance, perform hold and trip verification with controlled current ramps, and conduct a visual inspection for lead plating and dimensional tolerances; compare measured values and behavior directly to the datasheet acceptance criteria for pass/fail decisions.

Summary

This report highlights the polymeric resettable fuse’s role in circuit protection and reminds designers to verify three priorities in the datasheet before integration: electrical ratings (Ih/It/voltage), thermal/environmental limits and validated time‑current behavior. (Keyword: MF-RX012; include specs and datasheet references in procurement and test workflows.)

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP