-

- Contact Us

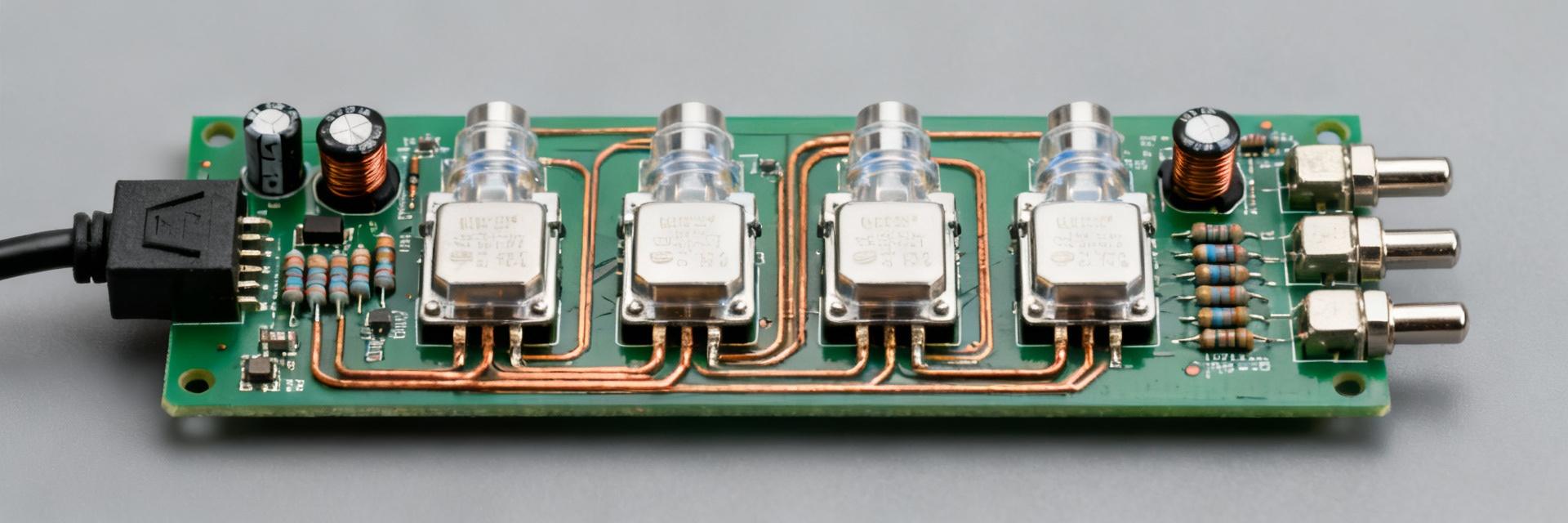

EL6257CU Datasheet Deep Dive: Specs, Pinout & Tests

The official two-page datasheet is compact but dense; it holds the electrical limits, pin assignments, and test cues an engineer needs to put a four-channel laser driver into service. This deep dive expands that terse document into a practical evaluation and integration guide, highlighting the datasheet key points, pinout interpretation, measurement methods, and real-world design tips. The article references the word datasheet where it clarifies how to translate table entries into bench actions and board rules.

Point: The goal is to convert specification tables into repeatable test procedures and robust PCB practices.

Evidence: The datasheet condenses absolute maximums, recommended operating conditions, and test circuits into a short format.

Explanation: By unpacking each block—power rails, output behavior, dynamic specs, and the pinout—engineers reduce risk during first-power and system integration phases.

H2: 1 — What is the EL6257CU? Device overview and key features (background)

H3: Device summary & typical applications

Point: The device is a four-channel laser-diode current driver with integrated oscillator functionality intended for bench and system-level use.

Evidence: It presents per-channel current outputs, a shared supply architecture, and an internal oscillator pin set for modulation and testing.

Explanation: Typical applications include laser diode arrays, fiber-optic transmitters, and automated test benches where synchronized multi-channel current control and fast modulation are required. The package suits both evaluation boards and compact system modules; the elevator pitch: “A compact, multi-channel current amplifier that centralizes control for small laser arrays.”

H3: High-level features to call out from the datasheet

Point: Five strengths stand out from the specification summary.

Evidence: (1) Four independent channels with matched behavior; (2) Per-channel output drive suitable for typical small-signal diodes; (3) Bandwidth adequate for moderate-speed modulation; (4) Defined common-mode and compliance voltage limits for safe diode operation; (5) Built-in oscillator for functional verification and modulation.

Explanation: Compared to generic multi-channel drivers, this device combines compact integration with integrated test/modulation capability, making it efficient for both prototype benches and low-channel-count production equipment.

H3: Ordering, packaging and part variants

Point: Package and handling notes materially affect assembly and reliability.

Evidence: The part is offered in a through-hole/package style suited to easy bench-soldering and system assembly; common ordering suffixes indicate revision or screening level. ESD sensitivity and storage recommendations are flagged in the handling notes of the datasheet.

Explanation: Early planning should include ESD controls, moisture sensitivity checks if a sealed package option exists, and correct marking verification on receipt. If multiple suffixes exist, select the variant that matches thermal and screening needs for the target product environment.

H2: 2 — Electrical specifications deep-dive (datasheet analysis)

H3: Power rails, supply currents and absolute maximums

Point: Understanding absolute-maximum vs recommended operating conditions prevents latent failures.

Evidence: The datasheet lists VCC, typical supply current, and absolute maximum ratings; a prudent design margin is advised (commonly 10–20% below absolute maxima).

Explanation: Practically, if VCC absolute max is X volts, set the nominal supply to X * 0.85–0.90 and validate under worst-case line tolerance. This derating extends lifetime and prevents single-event overstress during transients or assembly errors.

| Condition | Absolute Max | Recommended Operating |

|---|---|---|

| VCC | Absolute_Max_V | Absolute_Max_V × 0.85–0.90 |

| Supply current (per device) | Absolute_Max_I | Typical_I + margin |

| Storage/ESD | Specified Level | ESD control per handling notes |

H3: Output characteristics: current ranges, compliance voltage, and linearity

Point: Per-channel current capability and compliance voltage determine which diodes and load configurations are safe.

Evidence: The datasheet gives typical output current ranges, a compliance voltage that limits the maximum forward voltage across the diode, and linearity/accuracy spec columns.

Explanation: Engineers should read typical and min/max columns carefully: use guaranteed min/max for pass/fail criteria, and typical for design expectation. Example: if a channel lists 0–50 mA typical with compliance up to Vcomp, ensure the diode Vf under target current stays below Vcomp with margin for Vf variation.

H3: Dynamic performance: bandwidth, slew rate, noise and stability

Point: Dynamic specs govern modulation speed and signal integrity.

Evidence: Small-signal bandwidth, slew-rate, and noise density entries indicate how fast and how clean the current can be switched.

Explanation: For high-speed modulation, validate bandwidth with a swept sine test and check slew-rate limiting on edges. Noise density impacts low-current precision: measure noise RMS over the specified bandwidth and compare to datasheet figures. If noise exceeds spec, investigate decoupling, ground routing, and thermal effects as likely causes.

H2: 3 — Pinout & package orientation (pinout)

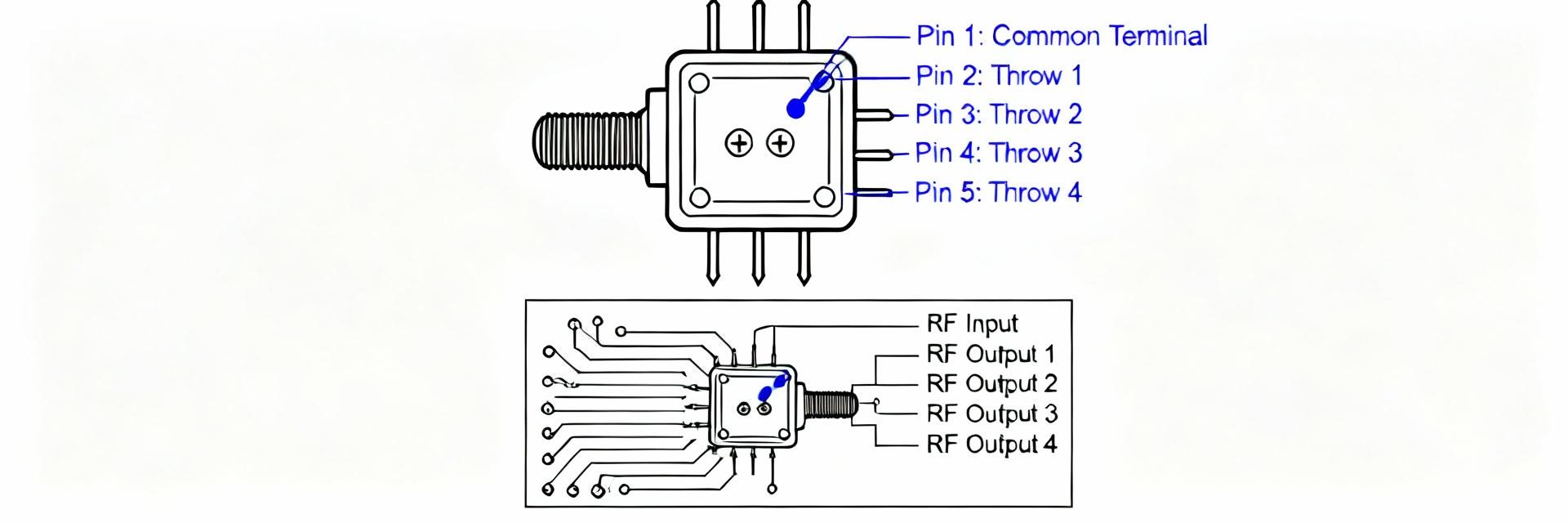

H3: Pin diagram and package orientation (how to read the drawing)

Point: Correct orientation interpretation avoids single-pin errors and catastrophic reverse connections.

Evidence: The top-view drawing in the physical section maps pin numbers to functions and a package key mark denotes Pin 1.

Explanation: Always correlate the PCB footprint silkscreen, the package key, and the assembly drawings before soldering. Recommended practice: place a polarized mark on the board and verify alignment under microscope prior to power-up. A labeled pinout graphic for the assembly and test jig is strongly recommended.

H3: Pin-by-pin function table with typical voltages/signals

Point: Each pin has expected DC bias and usage notes that must be respected.

Evidence: The datasheet lists pins such as VCC, GND, OUT1–OUT4, OSC input/output, compensation, and NC pins with recommended external components.

Explanation: Create a quick-reference table on the schematic with pin, function, expected idle voltage, and notes (e.g., “OUT pins: expect near-diode-forward-voltage under load; add series sense resistor for calibration”). Flag pins that need compensation capacitors or pull-ups to ensure stability and predictable startup.

H3: PCB footprint, layout & routing tips for reliable pin behavior

Point: Layout choices materially change noise, thermal, and stability behavior.

Evidence: Datasheet hints plus practical lab experience point to tight decoupling, single-point grounds for sensitive nodes, and short output traces.

Explanation: Place bulk decoupling close to VCC pins, use 0.1 µF ceramic in parallel with a 10 µF tantalum where recommended, and run dedicated ground returns for outputs. Use thermal vias under the device copper pad if continuous dissipation is expected. Checklist: decoupling within 2–5 mm of rails, output traces

H2: 4 — Test procedures & evaluation setup (method guide)

H3: Recommended bench schematic & BOM for evaluation

Point: A minimal, repeatable bench schematic shortens debug cycles.

Evidence: Test setups normally include VCC supply, series test resistors or calibrated diode loads, decoupling caps, and measurement taps.

Explanation: Essential BOM: regulated DC supply (programmable), 0.1 µF + 10 µF decoupling, low-inductance series resistors (for dummy loads), current-sense resistor (if measuring with DMM), oscilloscope with 50 Ω probe, current probe, and RF analyzer for bandwidth/noise. Wire short, keep loop areas small, and instrument grounds carefully to avoid measurement artifacts.

H3: Key tests to validate datasheet claims

Point: Follow stepwise tests to validate DC, compliance, dynamic, and noise specs.

Evidence: Standard procedures include DC output current verification, compliance voltage check, small-signal bandwidth sweep, slew-rate edge test, and noise spectral density measurement.

Explanation: For DC: ramp supply to recommended VCC and measure per-channel current into a calibrated dummy load; pass if within guaranteed min/max. For dynamic: inject a small-signal sine and measure –3 dB point. For noise: capture time-domain and compute RMS in the datasheet bandwidth. Record test conditions and repeat three runs to assess repeatability.

H3: Data recording, repeatability and interpreting discrepancies

Point: Systematic data logging separates marginal parts from setup issues.

Evidence: Repeatable deviations often indicate thermal runaway, layout parasitics, or measurement grounding errors.

Explanation: Log supply voltage, ambient temperature, probe types, and cabling. If results drift with time, suspect thermal buildup; if noise changes with probe orientation, suspect ground loops. Use averaging and statistical summaries (mean, stdev) to report results and define a pass/fail boundary tied to guaranteed datasheet limits.

H2: 5 — Design integration & practical application tips (method guide)

H3: Driving laser diodes safely: current limiting and protection

Point: Protection measures mitigate diode and driver failure modes.

Evidence: Practical measures include series resistors, clamp diodes, soft-start, and fast fuses where failure would be catastrophic.

Explanation: Use sense resistors and current watchdogs to detect overcurrent events; include reverse-bias protection and transient suppression on output lines. In the event of diode short or thermal runaway, the driver should be isolated by a crowbar or active current-limiting scheme to prevent sustained overstress.

H3: Power supply decoupling, grounding and EMI control

Point: Noise and EMI translate directly to output instability and measurement errors.

Evidence: Datasheet noise figures worsen with poor decoupling and large loop areas; EMI can induce spurious modulation.

Explanation: Place decoupling at the package pins, tie analog ground to chassis at a single point, and add ferrite beads on supply inputs if conducted emissions appear. For common-mode issues, small common-mode chokes on output bundles reduce radiated emission while preserving transient response.

H3: Thermal management and long-term reliability

Point: Continuous operation creates steady-state dissipation that must be managed.

Evidence: The datasheet provides power dissipation and junction temperature limits; exceed them and expect drift or failure.

Explanation: Provide adequate copper area, thermal vias, and consider a small heat spreader if multiple channels run near maximum. For high-duty cycles, derate current or add forced-air cooling. Monitor junction temperature in long-term soak tests to confirm reliability margins.

H2: 6 — Practical checklist, troubleshooting & resources (action recommendations)

H3: Pre-design checklist for engineers

Point: A short verification list eliminates common integration issues.

Evidence: Cross-checks on pin compatibility, voltage rails, max output current, and package fit reduce surprise failures.

Explanation: Verify mechanical footprint, confirm recommended decoupling, validate thermal plan, and ensure ESD safeguards are in place. Keep the original datasheet and revision notes on-hand during design reviews.

H3: Common failure modes and how to debug them

Point: Symptom-driven debugging speeds root-cause isolation.

Evidence: Examples: a dead channel often indicates a short or thermal shutdown; oscillation suggests compensation or insufficient decoupling.

Explanation: Stepwise diagnostics: isolate channel, replace load with dummy resistor, measure DC behavior, inject small-signal modulation, and swap in a known-good board to separate component from board issues. Use infrared imaging to spot thermal hotspots quickly.

H3: Useful references, compatible parts & next steps

Point: Decisions to keep, modify, or replace depend on measured performance versus system needs.

Evidence: Maintain a decision tree based on test outcomes: pass (keep), marginal (modify layout/decoupling), fail (replace with modern equivalent).

Explanation: After evaluation, document lessons learned, update BOM and footprint templates, and define acceptance criteria for production. Retain the datasheet PDF and the revision log as the authoritative reference for all future changes.

Summary

- EL6257CU is a compact four-channel laser-diode current driver with integrated oscillator and clearly defined electrical limits—prioritize derating and ESD controls in early design phases.

- Translate datasheet tables into three practical checks: DC current vs guaranteed limits, compliance-voltage headroom for diode Vf, and dynamic bandwidth/slew validation with controlled fixtures.

- Pinout and PCB layout largely determine real-world noise and stability—tight decoupling, short returns, and thermal vias reduce failures.

- Follow a structured test plan: bench schematic, BOM, repeatable measurements, and a documented pass/fail matrix before system integration.

- Use the practical checklist and troubleshooting flow to decide whether to keep, modify, or replace the part after evaluation.

H2: 7 — Common questions and answers

H3: How should an engineer verify the output current against the datasheet?

Measure with a calibrated current sense resistor or a current probe while running the device at recommended VCC and ambient temperature. Use a dummy resistor sized to draw the target current and verify each channel against guaranteed min/max values. Repeat measurements three times and log conditions—if values fall outside guaranteed limits, check supply voltage droop, layout grounding, and thermal effects before concluding a device failure.

H3: What are the key pinout checks to avoid miswiring on first power-up?

Confirm orientation using the package key mark and the PCB silkscreen, verify VCC and GND continuity, and ensure no OUT pins are shorted together. Check for required external components (compensation caps or pull-ups) and ensure NC pins are left floating as specified. Use a limited-current bench supply on first power-up and monitor supply current for unexpected draw.

H3: What bench equipment and settings produce reliable bandwidth and noise measurements?

Use a high-bandwidth oscilloscope with low-noise probes, a spectrum analyzer for noise density, and a current probe for transient edges. Terminate outputs correctly (50 Ω or high impedance per test case) and average measurements where appropriate. Record sampling rate, probe attenuation, and filter settings with each dataset to ensure repeatability and comparability to datasheet figures.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP