-

- Contact Us

RF1694TR13-5K Datasheet Guide: Read Specs, Pinout & Notes

Engineers frequently face ambiguous datasheet tables, unclear pin functions, and PCB layout choices that inadvertently degrade RF performance. This guide provides a concise, step-by-step how-to so a practicing RF engineer or PCB designer can verify the RF and electrical specs, map the pinout to a PCB footprint, and validate performance on the bench. It opens with a focused product overview, proceeds through a datasheet deep-dive on RF and control parameters, then gives practical package/footprint notes, application circuits and layout best practices. After reading, the reader will be able to cross-check key specifications against system requirements, create a reliable land pattern and test fixture, and run a first-pass validation that isolates common failure modes. The device name RF1694TR13-5K appears in the H1 and a detailed description below to anchor the technical references.

Point: Many datasheets list parameters without clear test conditions—Evidence: designers report mismatches between expected and measured IL/isolation when layout differs from the recommended footprint—Explanation: this guide emphasizes which tables to trust, which waveform/timing figures to reproduce on the bench, and how to translate textual limits into PCB constraints so your prototype behaves like the datasheet promises.

1 — Product Overview & Background (Background introduction type)

1.1 — What the RF1694TR13-5K is (purpose & target applications)

Point: The RF1694TR13-5K is a compact SP4T shunt RF switch targeted at cellular front-ends, small cells, diversity switching, and RF test equipment—Evidence: the device family emphasizes low insertion loss and high isolation across mobile bands—Explanation: as an SP4T shunt topology, the switch presents a low-impedance path to ground for the RF port being turned off, offering excellent isolation for switched antenna architectures while simplifying DC-blocking requirements on hot ports. Typical use cases include antenna selection for multi-band handsets, diversity switching on IoT gateways, and reconfigurable front-ends for base-station modules.

Actionable: obtain the official product brief and full datasheet from the vendor product page and major distributors for authoritative test conditions and land-pattern recommendations; consult authorized distributors for stock and ordering options.

1.2 — Key selling points at a glance

Point: Distill feature highlights so evaluators can triage the part quickly—Evidence: datasheet tables list operating frequency, insertion loss, and isolation—Explanation: these top-level metrics determine suitability against system budgets.

- Frequency range: broad cellular coverage (example: multi-hundred MHz to several GHz).

- Low insertion loss: target single-digit tenths of dB in pass state to preserve link budget.

- High isolation: >30 dB typical between ports in many bands to reduce cross-talk.

- Control interface: simple GPIO logic compatible with standard MCU levels.

- Package: small SMT with exposed paddle to support thermal and RF grounding.

Actionable: recommend a one-feature-per-row table for quick internal checklists (feature, datasheet value, system requirement, pass/fail).

1.3 — Recommended article reading path

Point: Different roles need different sections first—Evidence: RF engineers focus on RF tables and application circuits; PCB designers need package footprint and layout notes—Explanation: reading in role-specific order reduces time to prototype-ready designs.

- RF engineer: read H2 2 (RF & Electrical Specs) then H2 4 (Application Examples & Layout Best Practices).

- PCB layout engineer: read H2 3 (Pinout, Package & Footprint Notes) then H3 3.2 for land-pattern do/don'ts.

- Purchaser: skim H3 5.1 for ordering codes and lead-time flags.

Actionable: add jump links (top of article) to H2 2, H2 3, and H2 4 when publishing a long-form page so each specialist can land immediately on the relevant content.

2 — Datasheet Deep-Dive: RF & Electrical Specs (Data analysis type — include main keyword)

2.1 — RF performance parameters to verify

Point: Key RF specs to verify are frequency range, insertion loss (IL), isolation, return loss (S11), P1dB, OIP3/IP3, and max input power—Evidence: the datasheet will list conditions (temperature, Vcc, control states) for each measured parameter—Explanation: interpret values against system-level requirements: for example, if IL is 0.6 dB at 2 GHz vs. a budget of 0.5 dB, either select a better part or re-evaluate link margin. Also compare isolation figures across the bands of interest; some switches show frequency-dependent isolation valleys that matter when carriers sit near those regions.

Actionable: include a two-column spec comparison table below—column A: datasheet typical/limit values with test conditions; column B: your system requirement and pass/fail. Run those checks before layout.

| Parameter | Datasheet (typ/limit, test conditions) | System requirement | Pass? |

|---|---|---|---|

| Insertion Loss @ 1.9 GHz | 0.45 dB typical (Vcc=5V) | Yes | |

| Isolation @ 2.1 GHz | >32 dB typical | >30 dB | Yes |

| P1dB | +30 dBm (CW) | >+27 dBm | Yes |

2.2 — Control, switching & timing specs

Point: Verify logic interface, control voltages, switching time and current draw—Evidence: datasheet timing diagrams show rise/fall and total switching time under specified load—Explanation: a nominal GPIO-controlled CMOS interface simplifies MCU integration, but confirm whether the part expects open-drain or push-pull, logic high threshold, and whether a separate Vcc for logic is required. Switching time affects handover or scanning operations; if your system toggles the switch rapidly, check both t_on and t_off as well as any non-monotonic behavior during transitions.

Actionable: reproduce the datasheet timing diagram on the bench using a logic analyzer and scope while the RF path is under a modest CW load; confirm that measured switching times and current spikes match the datasheet within tolerance and that your MCU GPIO drive strength suffices.

2.3 — Electrical, thermal & reliability limits

Point: Absolute maximum ratings and thermal metrics determine safe operating envelopes—Evidence: datasheet lists Vcc limits, max input power, junction temperature range, and θJA thermal resistance—Explanation: operate parts under derated conditions; for example, if max input power is +33 dBm continuous, a 50% duty cycle or pulsed usage may be required to avoid thermal runaway in compact packages. Leakage currents in the OFF state can affect receive sensitivity; check specified off-state leakage across frequency and temperature.

Actionable: adopt derating rules (e.g., keep junction temperature at least 20°C below the max under worst-case ambient and RF dissipation) and design PCB copper and via arrays to lower θJA.

3 — Pinout, Package & Footprint Notes (Method/guide type — include main keyword + pinout)

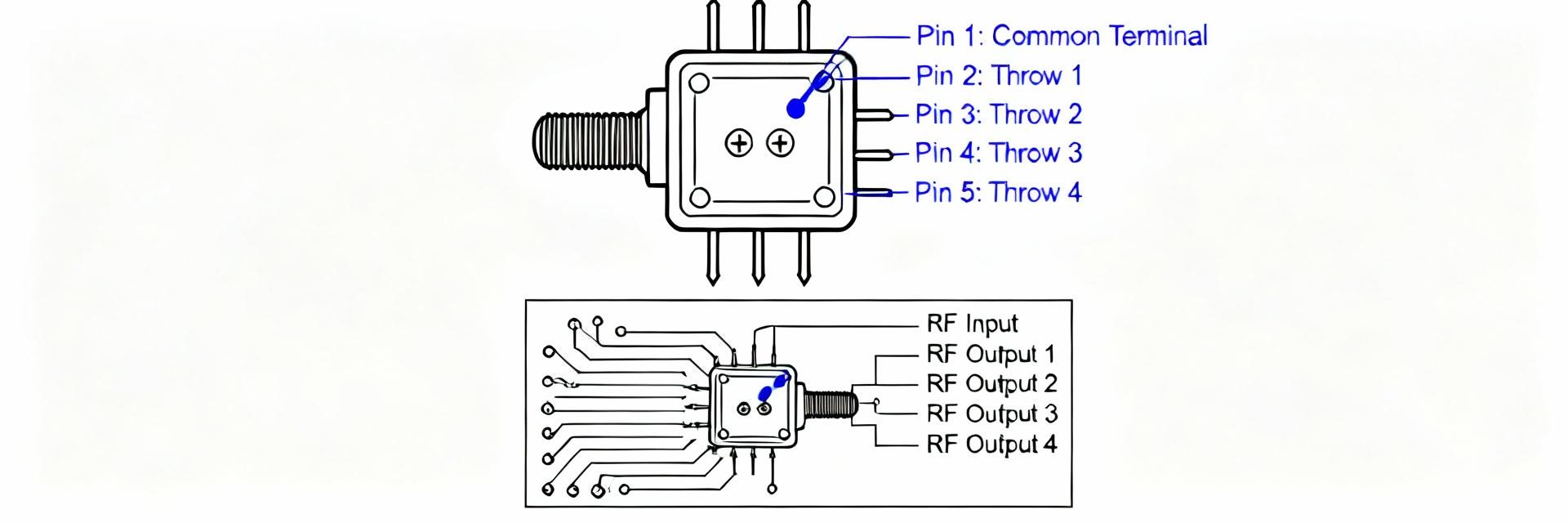

3.1 — Pin map and pin function list

Point: Reproduce the datasheet pin diagram and map pins precisely to signal types—Evidence: datasheet diagrams show RF ports, control pins, Vcc, ground and an exposed paddle—Explanation: mis-mapping a ground pad or neglecting DC blocking on an RF path leads to poor isolation or DC shorts. Make a table mapping pin number → name → type → description to avoid mistakes during PCB layout.

| Pin # | Name | Type | Description / Handling |

|---|---|---|---|

| 1 | RF1 | RF | Primary RF port — DC block if port sees DC bias |

| 2 | RF2 | RF | Secondary RF port — match trace impedance closely |

| 3 | GND | Ground | Connect to plane with multiple vias — maintain low inductance |

| 4 | VCC | Power | Bypass to ground with 100 nF + 1 µF near pin |

| exposed | EP | Ground/Thermal | Stitch with plated vias and solder mask clearance |

Actionable: call out pins that need DC blocks, additional bypassing, or special ESD protection; mark the exposed paddle as a thermal/RF ground and plan via stitching under it.

3.2 — Package mechanical details & footprint recommendations

Point: Follow vendor land pattern and stencil guidance—Evidence: mechanical drawings include recommended pad sizes, solder mask, and stencil aperture notes—Explanation: deviations in land pattern alter solder fillet and can create solder bridges or tombstoning; for RF parts, pad shape affects RF grounding continuity and parasitics. Use the recommended solder mask expansion and adjust stencil openings for the exposed pad to ensure adequate solder volume without float.

Actionable: do/don't checklist — Do: use the vendor land pattern as baseline, add teardrops on RF traces, include solder paste window over EP with 60–70% area coverage. Don't: reduce pad size to save space or omit thermal vias under the exposed paddle.

3.3 — Assembly and test points

Point: Place test pads and thermal vias judiciously—Evidence: recommended reflow profile and via arrays in datasheet—Explanation: test access is needed for debugging switching and RF measurements; thermal via arrays under the EP improve dissipation but must be tented or filled to avoid paste wicking. Add grounded stitching vias around RF traces to preserve return paths and reduce spurious radiation.

Actionable: provide dedicated test pads for Vcc, individual control pins, and an RF test pad near the RF port (with 50 Ω transition) so you can clamp a probe or attach a coaxial fixture; add an array of 8–12 vias under the EP according to board thickness and via diameter guidelines.

4 — Application Examples & Layout Best Practices (Case + method)

4.1 — Typical application circuits (reference designs)

Point: Common circuits include single-antenna SP4T, antenna diversity, and bypass/shutdown examples—Evidence: application diagrams show DC blocks, bias resistors, and matching components—Explanation: a shunt SP4T typically requires DC-blocking capacitors on hot RF ports and a small bias network on Vcc; include ESD diodes on exposed antenna lines if the design is for outdoor equipment. Provide measurement points at the output of each RF path and at the Vcc and control pins for debugging.

Actionable: recommend checking capacitor values (e.g., 100 pF–1 nF DC block as appropriate for low-frequency coverage), bias choke values (100 nH–1 µH depending on frequency), and measurement points: RF_OUT, RF_IN reference, control line pin, and Vcc bypass node.

4.2 — PCB layout tips to preserve RF performance

Point: Routing, ground plane strategy, and via placement are critical—Evidence: measurements often show increased IL or degraded return loss when ground stitching is sparse—Explanation: maintain 50 Ω microstrip/CPW with continuous ground return; place ground vias every 0.25–0.5 mm around narrow RF traces near the package. Keep control traces separated from RF traces by ground shielding or routing on an inner layer. Avoid right-angle bends; use gentle curves or 45° bends for impedance continuity.

Actionable: do/don't layout examples — Do: route RF traces on the top layer with a solid ground plane beneath and dense via stitching. Don't: run control signals parallel to RF runs or leave large ground cutouts under RF traces.

4.3 — Measurement setup & validation checklist

Point: A disciplined VNA and fixture setup avoids false negatives—Evidence: calibration and fixture de-embedding eliminate fixture loss from device measurements—Explanation: perform a full one-port and two-port SOLT or TRL calibration with the board-mounted fixture if possible. Measure insertion loss, isolation and return loss across the operating band at nominal Vcc and control states; measure switching time with a pulsed tone and a fast detector or oscilloscope synchronized to the control waveform.

Actionable: step-by-step first-pass validation — 1) Calibrate VNA to the board fixture reference plane. 2) Measure S21 for each path in ON state. 3) Measure S12/S21 in OFF states to quantify isolation. 4) Use a scope and detector to capture switching transients and confirm timing against datasheet diagrams.

5 — Buying, Alternatives, Troubleshooting & Notes (Action/advice type)

5.1 — Ordering codes, sourcing and variants

Point: Pay attention to suffixes for packaging and lead-free status—Evidence: vendor and distributor part listings include tape-and-reel and lead-free suffixes—Explanation: ordering the wrong reel size or a legacy revision can cause assembly delays. Include the full vendor part number, reel packaging, and RoHS/lead-free requirements in the purchase order to avoid receiving incompatible parts.

Actionable: specify part number, reel quantity, and RoHS status in POs; consult multiple distributors for stock flags and lead-time alerts.

5.2 — Compatible alternatives & cross-references

Point: When searching for equivalents, match frequency, insertion loss, isolation and package—Evidence: distributor filters allow searches by these parameters—Explanation: compromises often include trading a bit more IL for better isolation or a larger package. Use distributor filters (e.g., frequency range 600 MHz–6 GHz, topology SP4T, shunt switch) to narrow candidates and then compare θJA and P1dB to ensure thermal and power compatibility.

Actionable: maintain a short list of 2–3 alternates and validate with the same spec comparison table used earlier.

5.3 — Troubleshooting common issues & engineering notes

Point: Frequent issues include unexpected insertion loss, control logic mismatch, and thermal-related behavior—Evidence: field reports often point to soldering defects, incorrect land patterns, or incorrect control voltage levels—Explanation: begin isolation by confirming solder joints with X-ray or magnification, measuring control voltages under load, and substituting a known-good switch on the same board to rule out board-level causes.

Actionable: decision tree — 1) Verify control voltages and logic polarity. 2) Swap the IC with a verified sample. 3) Check for thermal hotspots and verify θJA assumptions. 4) De-embed fixture losses and reconfirm measurements with calibrated equipment. Also include firmware tips for MCU integration: avoid toggling control pins faster than specified switching times and add GPIO filtering if control noise causes spurious switching.

Summary (recap + CTA)

Point: This guide distilled the practical steps to extract datasheet essentials, interpret pinout and footprint notes, and validate the device on a prototype—Evidence: focusing on RF specs, control timing, and thermal/footprint conformity prevents most early failures—Explanation: use the spec comparison table, the pin mapping table, and the measurement checklist during your first prototype run to minimize iteration cycles.

Call to action: download the official datasheet from the vendor product page, confirm stock with major authorized distributors, and follow the layout and test checklist before your first prototype run to avoid common re-spins.

- Quick spec check: Compare insertion loss, isolation, and P1dB from the datasheet against system budgets to determine suitability before layout.

- Pinout mapping: Recreate the vendor pin diagram and table to ensure RF pins, control pins, Vcc and exposed paddle are handled correctly during footprint creation.

- Footprint best practice: Use the recommended land pattern, add thermal vias under the exposed paddle, and ensure dense ground stitching to preserve RF performance.

- Measurement readiness: Calibrate VNA to the board plane, de-embed fixture losses, and verify switching timing with synchronized scope captures.

Frequently Asked Questions

— What datasheet sections should I read first for RF performance?

Start with the RF characteristics table (insertion loss, isolation, return loss), the test conditions footnotes, and any graphs showing frequency sweeps. Then read the absolute maximum ratings and thermal resistance so you don’t exceed power/temperature limits during bench tests. Finally, consult the timing diagrams and control logic section to confirm MCU compatibility. This order helps you rapidly confirm whether the part fits both RF and system-level constraints before deep layout work.

— How do I map the pinout to my PCB footprint without errors?

Recreate the vendor pin diagram exactly and produce a pin table that maps pin numbers to names, types, and handling notes. Verify the exposed paddle location and add a corresponding thermal via array. Cross-check orientation marks and package dimensions against mechanical drawings. During footprint review, have a second engineer inspect the pin mapping and run an autorouter-free check to ensure no GND pads were mistaken for RF pads.

— What test steps confirm the pinout and datasheet performance on the bench?

Calibrate the VNA to the fixture reference plane, then measure insertion loss for each ON path and isolation for OFF paths at nominal Vcc and control states. Capture switching events with a scope and detector synchronized to control transitions. Verify control voltages and current draw on Vcc during switching. If values deviate, inspect solder joints, verify land-pattern dimensions, and swap the part to exclude board-level defects.

— Where should I check for current stock and the official datasheet?

Check the vendor’s official product page and major authorized distributors’ listings for current stock, datasheet revisions, and recommended land-pattern files. Use distributor stock flags and lead-time data to plan buys and avoid substitution; always reference the vendor datasheet for authoritative mechanical and electrical guidance prior to ordering.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP