-

- Contact Us

XRT7298IW Datasheet & Pinout: Complete Specs & Footprint

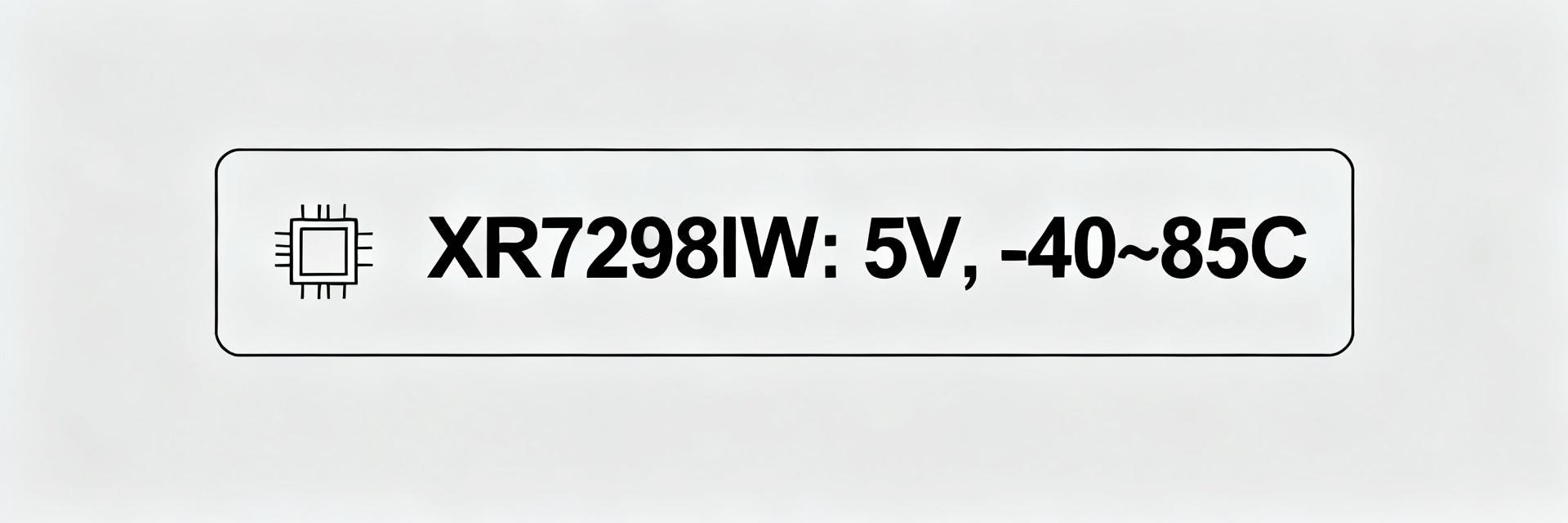

The XRT7298IW is a DS3/STS‑1, E3 line transmitter in a 28‑SOJ package with a nominal 4.75–5.25 V supply range; consolidating its datasheet, pinout, and footprint guidance into a single reference saves design time and reduces first‑pass PCB iterations. Evidence from manufacturer specifications shows the device targets telecom line interface and protocol mapping applications, so a focused guide that pairs electrical limits with layout and reflow notes helps PCB designers, QA engineers, and procurement teams avoid common pitfalls. This article summarizes the official datasheet highlights, provides a clear pinout map, and gives actionable footprint and integration checks for production readiness.

1 — Product Overview & Key Features (background)

What XRT7298IW Is (short definition)

Point: The XRT7298IW is a telecom‑grade line transmitter designed for high‑rate DS3/STS‑1 and E3 signaling; it comes in a 28‑lead SOJ package. Evidence: The device class and package are called out in product literature and the datasheet. Explanation: That combination makes the part suitable for line cards, protocol gateways, and repeater interfaces where a compact SOJ footprint and 5 V logic domain are expected; designers should treat it as a mid‑density, fixed‑function PHY that interfaces to both digital baseband logic and high‑speed line transceiver stages, so the datasheet must be consulted for timing and voltage domain boundaries before layout.

Headline Electrical Specs (quick spec table to include)

Point: Quick reference to the core electricals speeds up schematic review and BOM checks. Evidence: Key values drawn from the official datasheet indicate a recommended supply of 4.75–5.25 V, industrial operating range, and defined I/O domains. Explanation: The table below gives the most commonly referenced numbers designers check during schematic capture and power‑budgeting.

| Parameter | Typical / Range |

|---|---|

| Supply Voltage (VCC) | 4.75 – 5.25 V |

| Operating Temperature | −40 °C to +85 °C (industrial) |

| Typical Power Consumption | ~1.2 W (active, nominal) |

| I/O Voltage Levels | 5 V logic domain; control pins 3.3 V tolerant (verify datasheet) |

| Absolute Maximum VCC | 6.0 V (device level) |

Why It Matters for Designers (benefits & constraints)

Point: Package, voltage domain, and protocol support directly affect board layout and component choices. Evidence: A 28‑SOJ imposes pad pitch and keepout constraints; a 5 V domain requires attention to decoupling and thermal dissipation. Explanation: Designers must account for multiple supply pins, power plane partitioning, and thermal via strategy early in layout; the device’s role as a line transmitter means high‑speed differentials or legacy line signaling will interact with adjacent analog components and require careful cross‑section and impedance planning, so reviewing the datasheet alongside board stackup and placement rules prevents late design changes.

2 — Complete Electrical Specifications (data analysis)

Supply, Power & Thermal Details (numbers to highlight)

Point: Power and thermal metrics determine decoupling, copper allocation, and enclosure requirements. Evidence: The datasheet lists the recommended supply range (4.75–5.25 V), typical active power, and thermal resistance theta‑JA or theta‑JC values used to calculate junction temperature rise. Explanation: Use the device‑level theta‑JA together with worst‑case ambient and copper area to compute required derating; place bulk decoupling (10 µF) near the primary VCC entry and 0.1 µF ceramic caps at each VCC pin to minimize supply impedance at high frequencies. If the datasheet indicates a theta‑JA around typical SOJ values, designers should provision additional copper or thermal vias to keep junctions within rated limits under full load.

Timing, Interfaces & Signal Levels (protocol‑specific data)

Point: Timing and threshold figures dictate FPGA interface settings and line transceiver coupling. Evidence: The datasheet provides input/output thresholds, required setup/hold for control pins, and any driver impedance specs for DS3/STS‑1/E3. Explanation: When connecting to an FPGA or ASIC, ensure voltage domain translation where necessary and match series resistors to control overshoot on control lines. For the high‑speed links, follow datasheet guidance on line termination and coupling capacitors; verify PLL lock and clock sourcing requirements during bring‑up to avoid intermittent alignment issues between the transmitter and downstream line driver.

Absolute Maximums & Reliability Notes (safety margins)

Point: Absolute limits and ESD classifications set the safe operating envelope and handling rules. Evidence: The datasheet enumerates absolute maximum VCC, input voltage clamps, and factory‑specified ESD ratings (HBM/MM or equivalent). Explanation: Always apply conservative operating margins (for example, limit steady‑state VCC to the recommended band rather than the absolute maximum) and design ESD protection on exposed connectors. For reliability, choose capacitors and resistors rated for the operating temperature range and derate component voltage and power as recommended to maintain long‑term uptime in telecom environments.

3 — Pinout Breakdown & Functional Map (data + method)

Pin‑by‑Pin Table (recommended layout for the article)

Point: A concise pin table speeds wiring and CAD library creation. Evidence: The official pin descriptions list pin number, signal name, direction, and function — including multifunction pins and required pulls. Explanation: Below is a condensed example style you should replicate directly from the datasheet in your design notes; include exact net names in your schematic to avoid mismatches between silkscreen, component library, and PCB nets. The device pinout entries should be consulted for required pull‑ups/pull‑downs and any pins that are no‑connects for different package variants. Note: the full pinout must be transcribed verbatim from the datasheet into your CAD library.

| Pin | Name | Dir | Voltage Domain | Function |

|---|---|---|---|---|

| 1 | VCC | — | 5V | Primary supply |

| 2 | GND | — | 0V | Ground |

| 3 | TX_P | O | Line | Transmit positive differential |

| 4 | TX_N | O | Line | Transmit negative differential |

| … | … | … | … | … |

Tip: Ensure the pin table in your project files explicitly marks required strap states and default tie‑offs called out in the pinout section of the datasheet.

Power/Ground & Decoupling Best Practices (layout rules)

Point: Proper decoupling and ground strategy minimizes noise coupling and thermal hotspots. Evidence: The datasheet recommends decoupling per VCC pin and may show recommended capacitor values and placement. Explanation: Use a combination of 0.1 µF ceramics at each supply pin placed within 1–2 mm of the pin, plus at least one 10 µF bulk cap at the regulator output. Prefer a solid ground plane under the SOJ for return paths and star routing for sensitive analog domains only where the datasheet indicates separation. For power traces, size to carry required current and limit delta‑V; typical practice is to use at least 20–30 mil wide 1 oz copper traces for primary VCC runs and add thermal vias at the pads when extra heat dissipation is needed.

Special Pins & Configuration (mode pins, strap options)

Point: Mode pins and strap options control device startup and functional mode. Evidence: The datasheet documents strap combinations and any sequenced power requirements. Explanation: Document the default states you use in your schematic and add test points to verify strap states at first power; if the device requires a boot configuration or sequence, implement controlled ramping or supervisor monitoring. When straps are multifunction, add silkscreen notes and include populated solder jumpers for flexible configuration and field support.

4 — PCB Footprint & Mechanical Dimensions (method / actionable)

Recommended Footprint (land pattern and soldering notes)

Point: Land pattern fidelity reduces soldering defects and improves assembly yield. Evidence: The package mechanical drawing in the datasheet provides pad dimensions, pitch, and recommended solder mask clearance. Explanation: Implement the manufacturer recommended 28‑SOJ land pattern in your CAD library: use the exact pad length and width, match solder mask and paste aperture rules, and include a small chamfer if called out. For the central body, avoid placing tall components directly adjacent to the SOJ to prevent reflow shadowing. Note: provide an internal downloadable footprint file in your repository for consistent library use across teams.

Mechanical Drawing & 3D Model Tips (placement & keepouts)

Point: Mechanical constraints affect placement and cooling. Evidence: Datasheet package outline and seating plane dimensions specify maximum height and body extremes. Explanation: Reserve a keepout zone around the device equal to the maximum body extents plus a service margin; ensure the 3D model aligns with the seating plane so automatic collision checks in your CAD tool are valid. Add a 3D model to your library to verify component fit in the assembly and to catch potential interference with connectors or heatsinks prior to board fabrication.

Reflow & Assembly Considerations (manufacturing)

Point: Reflow profile and stencil design control solder joint quality. Evidence: The datasheet or application notes typically recommend a reflow temperature profile and note sensitivity to tombstoning or bridging. Explanation: Use a paste stencil with 60–80% pad coverage for SOJ leads (adjust per manufacturer paste recommendation), and follow the suggested peak temperature and soak profile. Specify inspection checkpoints for wetting and flatness on the internal leads; if bridging occurs in pilot runs, tweak paste aperture or reduce local paste volume and confirm board heating uniformity in the oven profile.

5 — Integration Examples & Troubleshooting (case study / method)

Example Schematic Snippet (how to wire it)

Point: Practical wiring examples speed prototype validation. Evidence: A minimal schematic should show VCC decoupling, series resistors for high‑speed signals, and any coupling/termination dictated by the datasheet. Explanation: Place 0.1 µF ceramics at each VCC pin, a 10 µF bulk at the regulator, series resistors (10–33 Ω) on control lines where the datasheet suggests dampening, and proper differential termination on TX outputs. Include a one‑line caption with the schematic: “Minimal interface wiring for XRT7298IW: VCC decoupling, differential terminations, and strap configuration for normal operation.”

Common Issues & Diagnostics (signal integrity, power faults)

Point: Early debug focuses on power, straps, and signal integrity. Evidence: Typical root causes include missing decoupling, incorrect strap states, and wrong land pattern dimensions causing cold joints. Explanation: Troubleshoot systematically: verify supply voltages at the device pins, confirm strap resistors and solder jumper states, inspect pads under microscope for wetting, and use an oscilloscope to check clock/PLL locking and line voltage waveforms. A logic analyzer can confirm configuration pin transitions during reset; check for thermal hotspots with an IR camera if power is higher than expected.

Test & Validation Checklist (what to verify on first power)

Point: A fixed first‑power checklist prevents missed failures. Evidence: Datasheet test points and recommended checks guide initial validation steps. Explanation: On first power, verify: (1) VCC rail within 4.75–5.25 V, (2) ground continuity and absence of shorts, (3) current draw matches expected typical power, (4) strap pin voltages correspond to selected mode, and (5) PLL or line interface achieves a lock or reports expected status. Document measurement points on the silkscreen to simplify bench validation.

6 — Procurement, Alternatives & Compliance (action recommendations)

Where to Find the Official Datasheet & Resources (links & verification)

Point: Always obtain the official datasheet and verify part status before procurement. Evidence: Manufacturer PDF and authorized distributor listings are primary sources for datasheet PDF, revision history, and RoHS/lead‑free declarations. Explanation: When sourcing the datasheet, confirm the revision and cross‑check RoHS and lead‑free markings for your region’s compliance. Maintain a local copy of the verified datasheet in your project repository and record supplier lot and date codes when ordering production quantities to trace any field issues back to a specific revision.

Pin‑for‑Pin Alternatives & Cross‑References (substitutes)

Point: Selecting a substitute requires matching pinout, electrical specs, and package. Evidence: Alternative devices exist but may differ in timing, supply domain, or mechanical outline. Explanation: When evaluating cross‑references, ensure pin‑for‑pin mapping, identical protocol support (DS3/STS‑1/E3), similar thermal characteristics, and compatible VCC. If a substitute requires a different footprint, plan PCB respin costs into the decision and test interoperability in a lab environment before committing to a BOM change.

BOM & Lifecycle Advice (EOL risks, inventory tips)

Point: Telecom parts can have limited lifecycle windows; plan for continuity. Evidence: Distributor lead times and manufacturer lifecycle notices indicate supply risk. Explanation: Adopt a multi‑supplier sourcing strategy, maintain safety stock for production ramps, and monitor manufacturer EOL notices. For long‑running products, qualify a second source early and maintain up‑to‑date footprints and schematic variants in your library so a replacement part can be validated with minimal redesign.

Summary

The XRT7298IW serves as a compact DS3/STS‑1 and E3 line transmitter in a 28‑SOJ package and the consolidated datasheet + pinout + footprint review presented here focuses on the critical integration points designers must get right: power domain management, decoupling and thermal planning, faithful pinout transcription into CAD, and a manufacturer‑recommended land pattern for reliable assembly. Before ordering prototypes, verify the official datasheet revision, confirm all strap and termination choices on the PCB, and run the outlined first‑power checklist to validate power, mode pins, and basic line functionality.

Key Summary

- XRT7298IW requires a 4.75–5.25 V supply and per‑pin decoupling to meet datasheet recommendations and ensure reliable operation.

- Accurate pinout transcription and adherence to the 28‑SOJ land pattern prevent assembly issues and signal integrity problems.

- Thermal planning and theta‑JA considerations determine copper area and via placement to keep junctions within rated limits.

- First‑power checks—rails, straps, current draw, and PLL/lock—catch most early integration faults before full functional testing.

Frequently Asked Questions

What voltage range should I use for the XRT7298IW according to the datasheet?

Follow the recommended operating range of 4.75–5.25 V for the primary VCC; treat the absolute maximum as a limit, not a target. Implement local decoupling at each VCC pin (0.1 µF) and a bulk 10 µF cap at the regulator output. Verify the voltage at the device pins on first power and monitor current draw against typical values noted in the datasheet to detect assembly or shorting issues.

How should I handle the XRT7298IW pinout in my CAD library to avoid mistakes?

Transcribe the pin‑by‑pin descriptions directly from the datasheet into your CAD library and use the exact net names in schematics. Mark required pull‑ups/pull‑downs and strap pins explicitly, and include silkscreen callouts for configuration resistors and solder jumpers. Add a mechanical 3D model and the recommended land pattern to the library so DRC and collision checks are accurate before fabrication.

What are the common assembly issues related to the 28‑SOJ footprint and how can I prevent them?

Tombstoning, bridging, and poor wetting are common with SOJ leads. Use the manufacturer’s recommended paste aperture coverage (typically 60–80%), ensure uniform oven profiling during reflow, and place small thermal reliefs or vias per the datasheet guidance if additional heat dissipation is needed. Pilot a small batch and inspect solder joints microscopically to confirm good wetting before full production.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP