-

- Contact Us

DSIC03LSGET Datasheet Checklist: Pinouts & Footprint

Industry reports show that footprint or pinout mistakes cause up to 30% of PCB re-spins and assembly delays. This article explains why a focused datasheet checklist prevents costly rework and accelerates time-to-market by giving you concrete verification steps for the DSIC03LSGET and its datasheet. The purpose is practical and actionable: a step-by-step checklist designers and purchasers can use to verify package details, pinout orientation, and the PCB land pattern before layout and assembly.

Point: A concise, data-driven pre-check reduces surprises in procurement and manufacturing. Evidence: multiple commercial assembly houses cite incorrect footprints and ambiguous pinouts as leading causes of first-article failures. Explanation: you’ll get prioritized checks that map datasheet dimensions and tolerances into CAD constraints, create verified footprints, and define a pre-production test plan that minimizes iterations.

1 — Product overview & package baseline (Background)

Point: Start by establishing the package baseline—its family, common variants, and suffix meanings. Evidence: manufacturer part strings and variant suffixes indicate mechanical differences (lead finish, pin count, orientation). Explanation: for the DSIC03LSGET, confirm the exact package string on the component label and BOM so you don’t mix families; a mismatch between a similar suffix can change pad size or thermal requirements and create late re-spins.

1.1 Package family & common variants

Point: Identify the package family and any manufacturer variants before footprint work. Evidence: parts with similar prefixes often share body outline but differ in plating or internal construction. Explanation: verify the part marking against your PO and request the official datasheet PDF or vendor drawing; search the datasheet for the phrase “package dimensions” and compare reference images to confirm the correct package variant before extracting pad geometry, because a different variant can shift pad-to-pad spacing or body tolerance.

1.2 Key electrical & mechanical specs to note first

Point: Capture must-check specs early: voltage/current ratings, contact resistance, insulation, operating temperature, and material/plating. Evidence: these specs determine dielectric clearance, pad metallurgy, and solderability. Explanation: note units in both imperial and metric for US production communications—e.g., 2.54 mm (0.100") pitch—so you and your contract manufacturer share the same dimensional expectations. Each electrical spec maps to constraints: high current requires larger copper area and thicker pads; high temperature rating impacts reflow profile choice.

1.3 Typical failure modes tied to package mistakes

Point: Common failure modes include misplaced pads, wrong pad size, and silkscreen interference. Evidence: assembly reports routinely list solder bridging, tombstoning, and poor wetting traced to incorrect land patterns. Explanation: mitigate with quick remedies—adhere to IPC footprint guidance (IPC‑7351B or equivalent) and request vendor-provided footprint files or recommended pad geometry. When in doubt, use the datasheet max dimensions for clearance and consult your assembler for pad paste percentages.

2 — Datasheet deep-dive: dimensions & tolerances (Data analysis)

Point: Accurate dimension extraction is the foundation for a reliable PCB land pattern. Evidence: ambiguous or overlooked notes in dimension tables lead to misplaced pads and mechanical interference. Explanation: parse dimension tables carefully, capture min/typ/max values, and convert tolerances into CAD DRC constraints so that your footprint generation uses conservative clearances and prevents late mechanical clashes.

2.1 Extracting critical dimension tables

Point: Extract pin pitch, pad-to-pad spacing, body length/width/height, and lead shape. Evidence: these geometric items define pad geometry and courtyard. Explanation: record min/typ/max values and default to max-body and max-lead extents when defining keepouts and component courtyard. For example, use pin pitch and pad-to-pad spacing to compute pad center coordinates; verify pad length against recommended land pattern callouts in the datasheet to set pad size and shape.

2.2 Interpreting tolerances & notes

Point: Tolerance callouts and general notes (e.g., “unless otherwise specified”) change how you use table values. Evidence: datum references and footnote symbols can shift critical dimensions. Explanation: translate table tolerances into CAD constraints (min pad clearance, maximum component body extents). If a dimension is listed as 2.54 ±0.05 mm, set your DRC to allow the component at the ± tolerance extremes; treat tolerance notes as drivers for assembly clearance and silkscreen offsets.

2.3 Verifying 3D model and mechanical fit

Point: A validated 3D STEP model prevents enclosure and placement surprises. Evidence: mechanical interference is a common late-stage failure when 3D checks are skipped. Explanation: obtain or build a STEP model from datasheet dimensions, check component height against enclosure keepouts and pick-and-place nozzle clearance, and include the 3D model in your ECAD so MCAD/ECAD integration flags any collisions before release.

3 — Pinout mapping & functional verification (Method / Data)

Point: Confirm pin numbering and orientation to avoid functional failures. Evidence: misoriented parts or swapped power/ground pins can destroy devices or boards. Explanation: cross-compare symbol, mechanical drawing, and the recommended PCB footprint to ensure the numbered pins in the schematic symbol map identically to the footprint pads in the PCB editor.

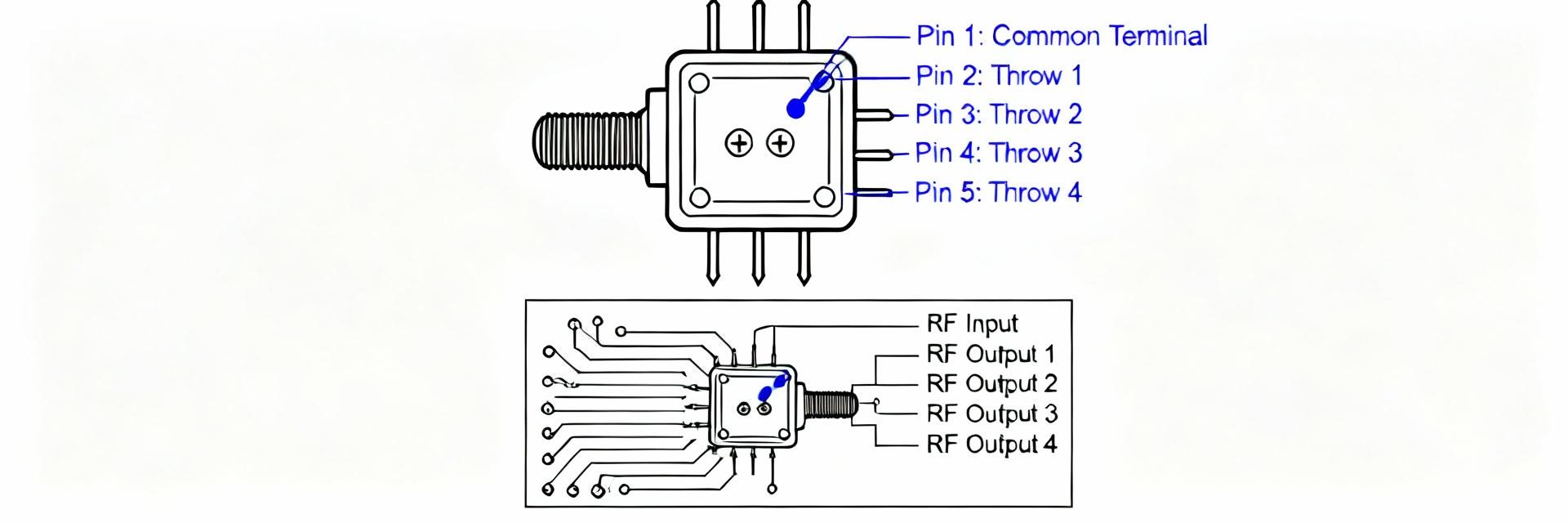

3.1 Confirming pin numbering & orientation

Point: Verify pin‑1 markers and orientation marks using all datasheet views. Evidence: datasheets show top and bottom views that must be reconciled with schematic symbols. Explanation: use three-way verification—symbol pin numbering, mechanical drawing orientation, and the footprint silk/top view—so you confirm pin 1 location, body chamfers, or notch markers. Document orientation in assembly notes and on the silkscreen if helpful to the assembler.

3.2 Functional pin assignments & electrical constraints

Point: Map power, ground, signals, and NC pins and capture routing requirements. Evidence: datasheet functional tables and electrical characteristics specify which pins need isolation or special routing. Explanation: identify pins that need keepouts, ESD protection, or controlled-impedance routing (differential pairs). For pads connected to ground or thermal pads, plan copper pour ties and thermal vias to meet both electrical and solderability goals.

3.3 Common pinout pitfalls & verification checklist

Point: Run a concise pinout verification checklist. Evidence: recurring issues include NC handling, thermal pad miswiring, and lack of test access. Explanation: verify NC treatment (do not route or tie unless the datasheet authorizes), map thermal pad requirements, ensure test pins or programming pads are accessible, and plan a first‑article electrical test: continuity, shorts, and basic powering procedures before full assembly.

4 — Footprint & land pattern creation (Method / How-to)

Point: Footprint creation translates datasheet geometry into pad shapes, paste rules, and silkscreen. Evidence: IPC‑aligned land patterns reduce solder defects and improve assembly yield. Explanation: derive pad geometry from datasheet dimensions, apply paste aperture recommendations, and ensure silkscreen and courtyard avoid pad solder areas to prevent contamination or misplacement during reflow.

4.1 Pad geometry, solder mask, and paste layer rules

Point: Define pad shape, pad size, and paste aperture percentages explicitly. Evidence: improper paste amounts cause tombstoning and insufficient fillets. Explanation: use recommended pad sizes from the datasheet or IPC table; for SMD leads, set paste aperture to 60–85% of the pad area as a starting point and adjust based on assembly house feedback. Ensure silkscreen is offset from pads and courtyard reflects max component extents.

4.2 Thermal & mechanical considerations

Point: If the package includes thermal pads or tabs, plan via strategy and copper tie patterns. Evidence: thermal pads without adequate vias or reliefs cause poor solder joint formation or thermal imbalance. Explanation: specify via diameter, via count, and via tenting rules; use thermal relief or spoke patterns for manual rework capability and coordinate with your assembler on via plating process for reliable solder wicking control.

4.3 Producing and validating footprint files

Point: Validate footprints in your ECAD workflow using DRC and 3D overlays. Evidence: cross-tool inconsistencies (units, origin points) create shifted footprints. Explanation: import measured dimensions, run DRC against your CAD ruleset, attach the 3D model to the footprint, and export Gerbers for overlay comparison. Send footprints to your assembly house for sign-off before releasing fabrication files.

5 — Verification, testing & pre-production checklist (Case study → Action)

Point: A formal pre-production checklist and test plan prevent assembly surprises. Evidence: structured first-article checks reduce iterative runs. Explanation: use a staged verification path—pre-layout confirmation, post-layout DRC and assembly review, then sample assembly and electrical verification—so you catch mechanical, soldering, and functional issues before full production.

5.1 Pre-layout verification steps

Point: Complete critical verifications before committing to layout. Evidence: parts measured off reel or samples often reveal deviations from nominal datasheet values. Explanation: confirm datasheet version, measure sample parts dimensionally, confirm pad geometry with the BOM item, and verify pick-and-place nozzle compatibility. Sign off these items with supplier or internal QA to establish traceability before layout.

5.2 Assembly & reflow test plan

Point: Define assembly tests and acceptance criteria for the first article. Evidence: oven profile verification and solder fillet inspection catch thermal or paste distribution issues early. Explanation: run a sample board with a validated reflow profile, inspect solder fillets visually and by X‑ray where joints are hidden, and apply acceptance criteria (wetting, fillet shape, absence of bridging). Document rework steps and when to trigger a board re-spin.

5.3 Supplier & manufacturing handoff notes

Point: Communicate precise handoff documentation to your BOM and manufacturer. Evidence: missing footprint sources or ambiguous orientation notes lead to mis-assembly. Explanation: include footprint source, attached 3D model, orientation marks, paste layers, and explicit notes such as “Do not invert” in BOM and Fab/Assembly notes; request manufacturer confirmation on SLA items like lead finish, reel orientation, and minimum order quantities.

6 — Quick-reference checklist & troubleshooting guide (Action recommendations)

Point: Provide a printable on-board checklist and immediate mitigation steps for common failures. Evidence: rapid triage reduces downtime on assembly lines. Explanation: segregate mandatory checks (datasheet version, pad geometry accuracy) from recommended checks (3D model fit, silkscreen clarity) and provide clear escalation steps if issues are found during assembly.

6.1 One-page printable DSIC03LSGET checklist

Point: Produce a one-page checklist grouped by datasheet, mechanical dims, pinout, footprint, paste/mask rules, and testing. Evidence: single-page checklists improve compliance during handoffs. Explanation: mark items as mandatory (e.g., confirm datasheet revision, pad size on CAD) versus recommended (3D model validation). Keep the checklist with release documentation and the BOM so assemblers can refer to it at intake.

6.2 Troubleshooting FAQ for common issues

Point: Provide quick Q&A for immediate fixes when problems surface. Evidence: common scenarios include wrong footprint, misaligned pads, tombstoning, and insufficient paste. Explanation: immediate mitigations include halting the run, performing a focused visual/X‑ray inspection, adjusting paste aperture or reflow profile, and scheduling a re-spin only after root-cause verification. Document findings and corrective actions for continuous improvement.

6.3 Long-tail keywords & SEO placement plan

Point: For published content, place long-tail phrases naturally in headings, lead paragraphs, and image alt text to aid discovery. Evidence: strategic placement in the first 100 words and in descriptive alt text improves search relevance. Explanation: incorporate phrases such as “DSIC03LSGET footprint dimensions” or “DSIC03LSGET pin numbering” into captions and metadata while keeping technical accuracy so readers and search engines find the content without sacrificing clarity.

Summary

- Verify datasheet dimensions and tolerances by extracting min/typ/max values and translating them into CAD DRC constraints; using the max extents for clearances reduces mechanical interference risk and informs pad size and pad placement decisions for the DSIC03LSGET.

- Confirm pinout orientation and functional assignments by cross-referencing symbol, mechanical drawing, and recommended footprint; document NC handling, thermal pad connections, and any ESD or controlled-impedance routing requirements.

- Create an IPC-aligned footprint with appropriate pad geometry, paste aperture, and silkscreen clearance; validate with a 3D model and obtain assembler sign-off to avoid re-spins.

- Run the pre-production checklist and assembly tests—oven profile validation, visual/X-ray inspection, and first-article electrical checks—to catch solderability or functional issues before full production.

Frequently Asked Questions

1 — How do I treat NC pins when creating a footprint or routing board for this datasheet?

Point: Treat NC pins cautiously. Evidence: datasheets sometimes change NC status between revisions. Explanation: do not connect NC pins unless the datasheet explicitly permits tying them to a net; leave them unconnected or mask them out in the footprint. If the assembler requests NC ties for stability, document that change and confirm the electrical impact with the component supplier.

2 — What pad size and paste percentage should I start with when implementing the PCB land pattern?

Point: Start from datasheet recommendations or IPC guidance. Evidence: paste volume typically correlates with pad size and component mass. Explanation: use the datasheet‑recommended pad geometry when present; otherwise follow IPC‑7351B guidance. For paste, begin around 60–80% aperture coverage for typical SMD pads and adjust after a sample reflow test; document results and iterate with your assembler.

3 — If I discover a footprint error after assembly, what immediate steps should I take?

Point: Rapid triage minimizes scrap. Evidence: immediate inspection can distinguish assembly process issues from footprint design faults. Explanation: halt production, sample-inspect affected boards (visual and X‑ray where needed), isolate root cause (footprint vs. process), and implement containment (adjust paste stencils, local rework) while preparing a controlled re-spin if the footprint is at fault. Record corrective actions and update the checklist for future runs.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP