-

- Contact Us

74F11D Datasheet: Complete Pinout & Electrical Specs

For high-speed TTL applications and legacy boards, the 74F11D (triple 3-input AND gate) remains a go-to logic element due to its fast switching and predictable drive characteristics. This concise, data-driven guide centralizes the 74F11D datasheet essentials so engineers can read pinout at a glance, size decoupling, interpret timing, and validate boards efficiently.

This guide is written for hardware engineers, firmware/hardware debuggers and students who need actionable numbers and step-by-step checks. After reading, the reader will identify pins quickly, select decoupling and layout practices, perform bench timing checks, and decide on suitable replacements or buffering strategies for production readiness.

Background

What the 74F11D is and common uses

The device implements three independent 3-input positive-AND gates in a fast TTL family style. Each gate produces Y = A·B·C with typical TTL input thresholds and moderate output drive capable of sinking more than sourcing in common scenarios. Typical uses include glue logic, high-frequency gating, bus control and legacy board repairs where deterministic TTL timing is required.

Quick reference spec table

| Parameter | Typical / Recommended |

|---|---|

| VCC (nominal) | +5.0 V |

| Input VIH / VIL (typ) | VIH ≈ 2.0 V, VIL ≈ 0.8 V |

| Propagation delay (tPD) | ~6–12 ns (depends on load) |

| Output drive (IOH / IOL) | IOH limited, IOL higher (sinking favored) |

| Packages | DIP (14-pin), SOIC (14-pin) typical |

Pinout

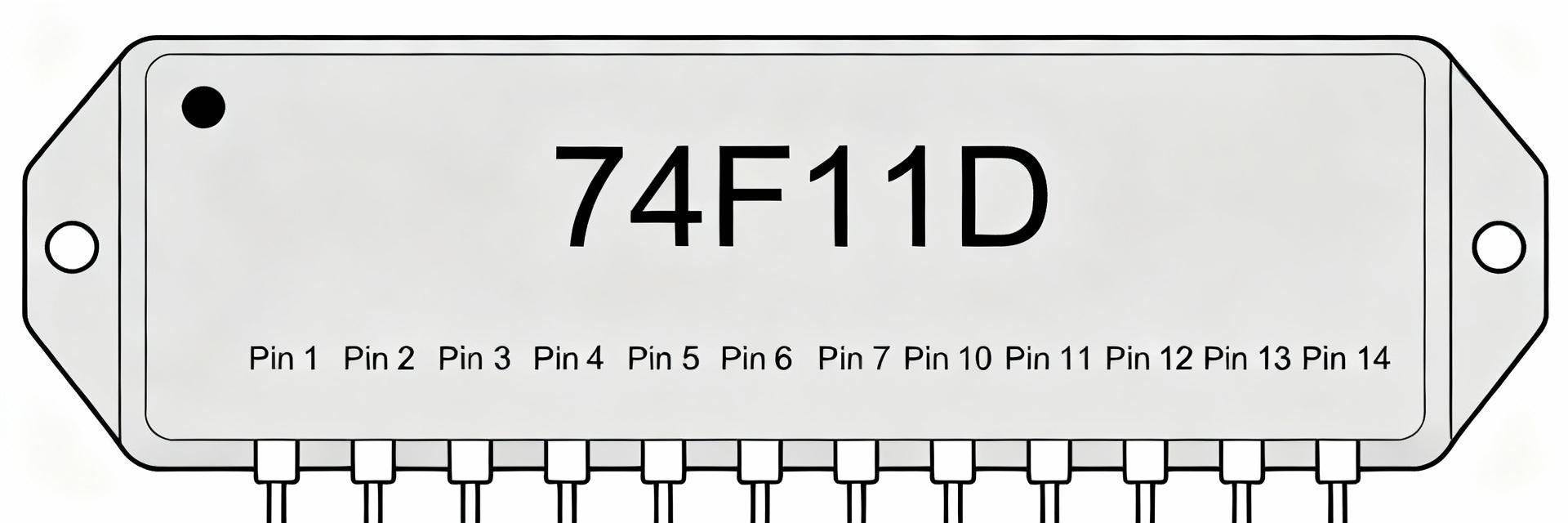

Pin-by-pin mapping and functional diagram

Typical pin map: three gates with inputs A1/A2/A3 → Y1, A4/A5/A6 → Y2, A7/A8/A9 → Y3; plus VCC and GND. Unused inputs must not float — tie to defined logic. The 74F11D pinout follows standard 14-pin bipolar logic conventions; identify VCC pin and notch/index before soldering to avoid misorientation and damage.

Pin map (14-pin DIP example): 1 A1 2 A2 3 A3 4 Y1 5 A4 6 A5 7 A6 8 Y2 9 A7 10 A8 11 A9 12 Y3 13 GND 14 VCC

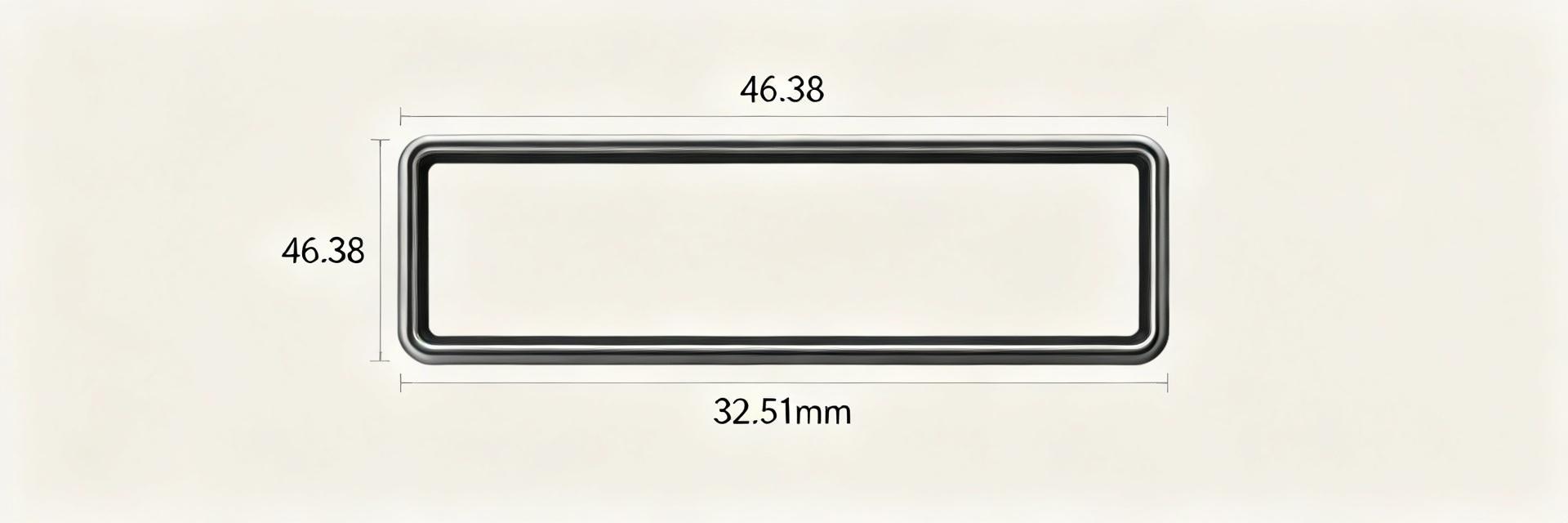

Package mechanical drawing and PCB footprint guidance

Common packages are through-hole DIP and surface-mount SOIC. For SOIC land patterns, use 0.65 mm pitch pads with thermal solder fillet allowance. Recommend 0.3–0.4 mm pad extension, solder mask clearance, and a clear orientation marker. Avoid excessive reflow dwell—these bipolar parts are sensitive to prolonged high temperatures.

Electrical specs

Absolute maximum ratings and recommended operating conditions

Absolute maximum: VCC should never exceed typical +6.5 V; inputs and outputs limited to VCC±0.5 V tolerance. Storage and junction temps must stay within datasheet absolute limits to avoid irreversible damage. Recommended operating VCC is +5.0 V ±5%; ambient range depends on temperature grade — observe derating for high-temperature environments.

DC characteristics: input/output thresholds, currents, and power

Read DC tables carefully: input thresholds (VIH/VIL) establish valid logic margins; input leakage and output voltages at specified IO determine noise margin and fan-out. Quiescent ICC may increase under elevated temperature or with switching; use these electrical specs to compute margin: margin = VIH(min) - VIL(max) and ensure system-level thresholds remain separated.

Timing & performance

Propagation delay, transition times and timing diagrams

Define tPLH/tPHL, rise/fall times (tR/tF) under specified load and VCC to interpret AC tables. Typical tPD values span single-digit to low tens of nanoseconds depending on load; measure with a 10 pF–50 pF load when comparing to datasheet. For cascaded gates, add worst-case tPDs plus margin when calculating setup and hold windows.

Fan-out, drive capability and noise margin

Fan-out is determined by input current and output drive: TTL families often assume smaller fan-out for high-speed devices. Compute fan-out = IO(sink/source capability) ÷ II(input current) and include noise margin from thresholds. For high-speed nets, consider buffering or series termination to control ringing and reflections on longer traces.

Application & design guidance

Typical circuits and interfacing examples

Common patterns: single-gate logic for gating clocks or strobes, outputs combined via OR before buffering (with care), and level shifting when interfacing to 3.3 V CMOS using series resistors and pull-ups. When mixing voltages, add clamping or buffer stages to prevent injection into TTL inputs, and prefer open-collector buffering for wired-OR patterns.

PCB layout and power integrity recommendations

Place a 0.1 µF ceramic decoupling capacitor near VCC–GND pins within 5 mm; add a bulk 1 µF nearby for board-level transients. Route VCC and GND with low-impedance returns, keep signal traces short, and avoid crossing high-speed traces near gate inputs. Thermal density rarely critical for single 14-pin parts but watch clustered footprints.

- Layout checklist: decoupling close to pins, clear orientation marker, short input traces, series terminations for >10 cm high-speed traces.

Testing, debugging & replacement

Bench tests to verify pinout and electrical behavior

Step-by-step: 1) continuity check orientation and VCC/GND. 2) Power up with current-limited supply and measure quiescent ICC. 3) Apply known logic vectors and verify outputs with a logic probe or scope. 4) Measure propagation delay with scope (50% points) under datasheet load. Observe current limits to avoid latch-up.

Common failure modes and repair/replace considerations

Failures include stuck outputs, elevated ICC or intermittent switching. Isolate by removing load or replacing suspect gate with a socketed part. When replacing, document package type, temperature grade, and part marking to ensure pin compatibility. Buffer noisy outputs and prefer replacement families only after verifying timing and drive trade-offs.

Summary

Key numbers live in the device DC and AC tables: nominal VCC, VIH/VIL, tPLH/tPHL, IOH/IOL, and ICC. Use the pinout map when orienting parts, place decoupling within millimeters, and run the bench checks above to confirm behavior before production. Consult the component’s official datasheet for absolute maximums prior to deployment.

Key summary

- The 74F11D datasheet central figures: VCC +5 V nominal, VIH ≈ 2.0 V, VIL ≈ 0.8 V, and tPD in the single-digit to low-double-digit nanoseconds. Use these for margin and timing chains.

- Pin handling and layout: tie unused inputs to defined levels, place a 0.1 µF decoupler within 5 mm of VCC–GND, and orient using the package index to prevent misinstallation.

- Testing checklist: continuity and orientation, current-limited power-up, static voltage checks on inputs/outputs, and oscilloscope timing for tPLH/tPHL with the datasheet load to validate performance.

FAQ

Is the 74F11D compatible with 3.3 V logic inputs?

Direct compatibility is marginal: VIH on classic TTL families expects ~2.0 V, so many 3.3 V CMOS outputs will register high but input current and undefined intermediate voltages can stress the device. Use level shifters or series resistors with clamping if certainty and long-term reliability are required.

How do I size decoupling for the 74F11D?

Place a 0.1 µF ceramic directly across VCC and GND pins for high-frequency transients and a 1 µF–10 µF bulk capacitor nearby for board-level stability. For dense switching, add local bulk capacitance and ensure low-impedance ground return paths to minimize supply bounce affecting logic thresholds.

What quick checks indicate a damaged 74F11D?

Symptoms: excessive ICC on power-up, outputs stuck at rail irrespective of inputs, or abnormal heat. Isolate by removing loads, check VCC for shorts, and swap with a known-good device. Record package type and markings before ordering replacements to guarantee pin and thermal compatibility.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP