-

- Contact Us

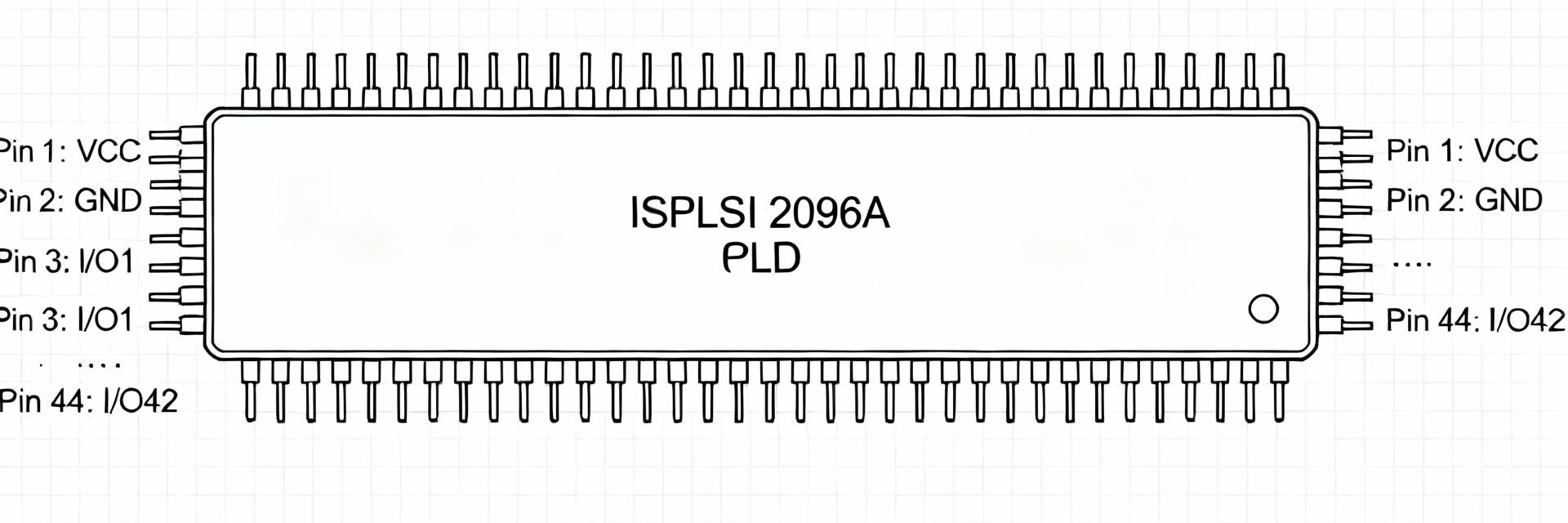

ISPLSI 2096A CPLD: Complete Datasheet & Pinout Guide

The ISPLSI 2096A is a mid-density CPLD offering roughly 96 macrocells and about 96 usable I/O pins, operating from a nominal 5 V rail (typical 4.75–5.25 V) with propagation delays down to ~7.5 ns depending on speed grade. These metrics matter because pin count drives board routing and connector choices, macrocell density limits local logic packing, and timing characteristics determine whether the part meets system-level timing requirements.

This guide consolidates the most used datasheet essentials, a full pinout walkthrough, package and timing details, integration best practices, and a compact design checklist to speed development. It is intended as a practical companion to the official datasheet and not a replacement for absolute electrical ratings.

Product overview & key specs (background)

Core architecture snapshot

Point: The device implements a fixed array of macrocells and I/O resources designed for glue logic, bus bridging, and control functions. Evidence: Typical device documentation lists ~96 macrocells with dedicated product macrocells paired to I/O banks. Explanation: For designers a “macrocell” represents the atomic combinational+registered resource; the macrocell count and I/O availability determine whether multiple small state machines or several bus interfaces can comfortably fit on the CPLD.

Package and variant summary

Point: Multiple package and speed variants exist to match thermal and timing needs. Evidence: Common offerings include PQFP/TQFP variants and several speed grades across the 5 V family with industrial temperature options. Explanation: When selecting a package, consider VCC range (4.75–5.25 V typical), thermal derating for your PCB, and the practical availability of the speed grade; check the official datasheet for full package option tables and obsolescence notes.

Pinout & package pin map (data / technical)

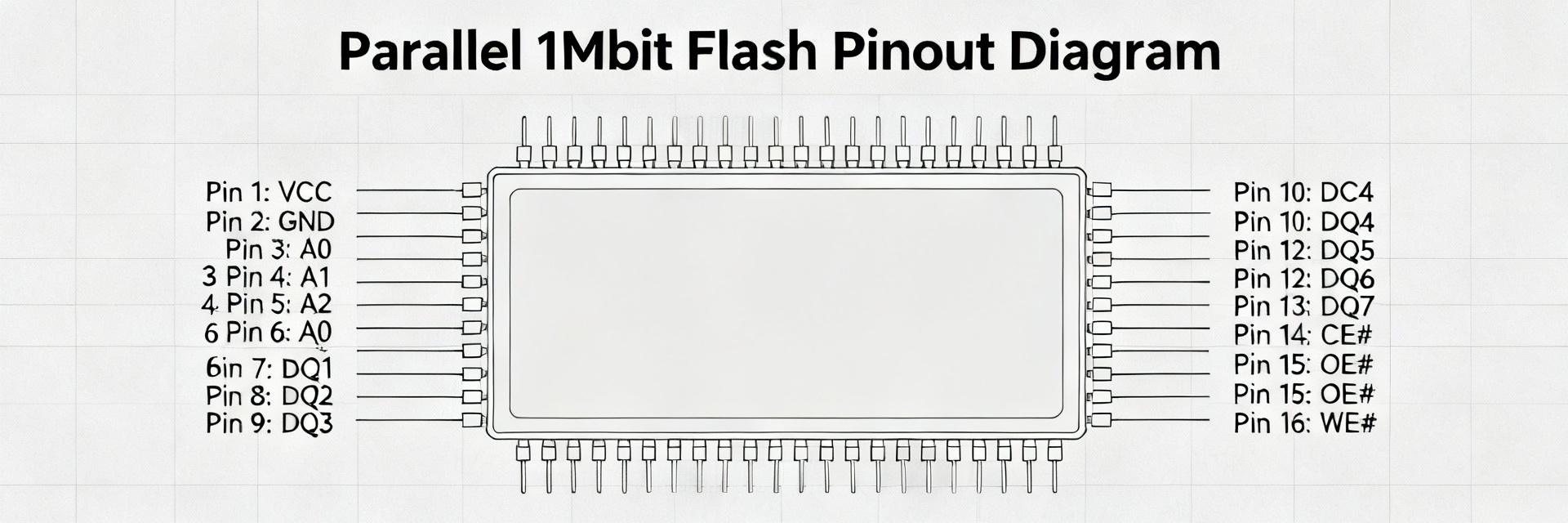

Pin grouping and functions (power, GND, I/O banks, config pins)

Point: Pins are grouped into power, ground, I/O banks, configuration, and programming connectors. Evidence: The standard pin set includes VCC/VCCO pins for core and I/O, VSS/GND returns, dedicated configuration pins (nCONFIG, nSTATUS/STATUS, CONF_DONE/DONE), and JTAG/programming signals. Explanation: Understanding ISPLSI 2096A pinout conventions — how I/O banks share VCCO, which pins are non-5 V tolerant, and which pins control configuration — is essential for reliable boot and proper level translation design.

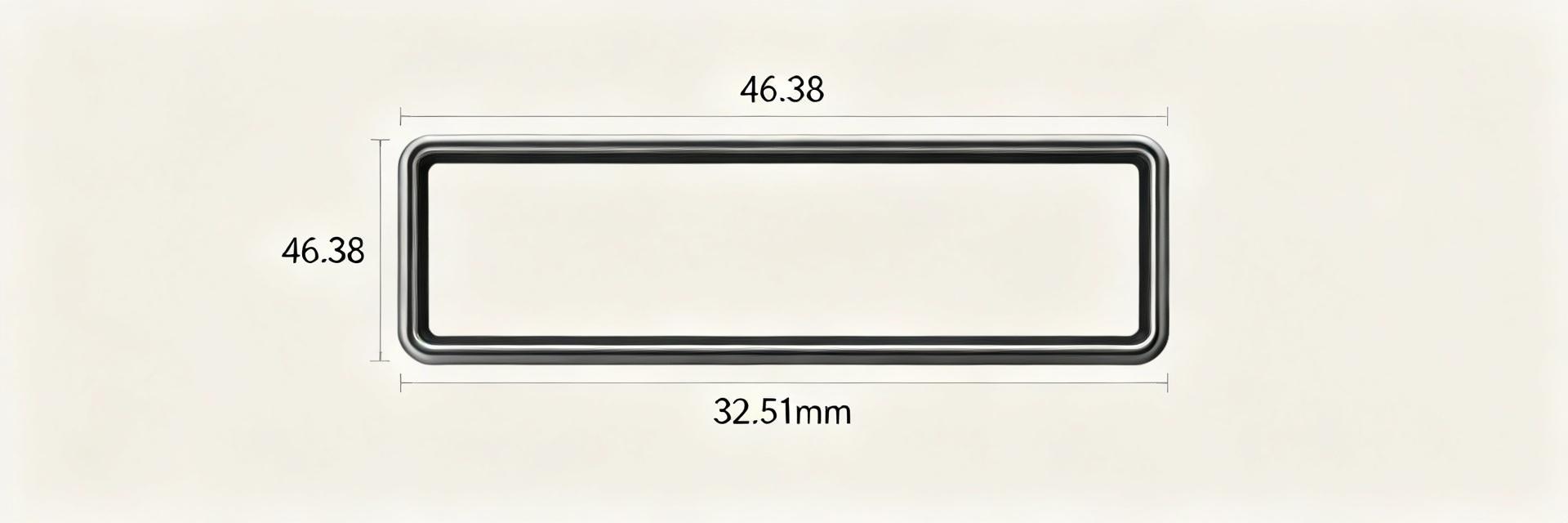

Representative pin numbering for a 128-pin QFP (how to read package drawing)

Point: Pin numbering follows a clockwise flow from the pin 1 marker on PQFP/TQFP outlines. Evidence: Typical 128-pin QFP drawings mark pin 1 and show sequential numbering around the package with clustered power pins. Explanation: Designers should wire power rails and GND first (observe VCC/VSS placement), mark the pin‑1 silkscreen, and ensure configuration pins and JTAG connectors are accessible before routing dense I/O to avoid rework; including a labeled schematic-style diagram and a CSV pin table in project assets is recommended.

Electrical characteristics & timing (data / analysis)

Power, current, and decoupling recommendations

Point: Proper decoupling and power sequencing are critical to avoid latch-up or failed configuration. Evidence: Device documentation cites VCC range near 5 V with both static and dynamic current figures that vary by speed and activity. Explanation: Use multiple decoupling capacitors (0.1 μF close to each VCC pin plus 10 μF bulk on the rail), route ground with a solid plane, and sequence core and I/O rails per datasheet guidance — power the core before or with I/O depending on family notes to ensure predictable configuration.

Timing parameters and I/O specs

Point: Propagation delays and I/O standards dictate usable clock rates and interface compatibility. Evidence: Propagation delay (tpd) values vary by speed grade, with typical low-end values around several nanoseconds and maximum toggle rates specified per I/O standard. Explanation: For timing closure, budget tpd plus board trace delays and external device setup/hold times; bench measurement with a scope and controlled test vectors helps validate timing margins before finalizing the design.

Integration & PCB best practices (method / how-to)

Schematic & PCB footprint tips

Point: A disciplined symbol and footprint strategy reduces layout errors. Evidence: Best practice examples show star power routing, decoupling close to pins, and clear silkscreen markers. Explanation: Name symbols consistently, place decoupling capacitors within 2–3 mm of VCC pins, use a continuous ground plane, route sensitive clock lines away from switching power traces, and include pin‑1 silkscreen plus testpoints for critical nets like clocks and configuration signals.

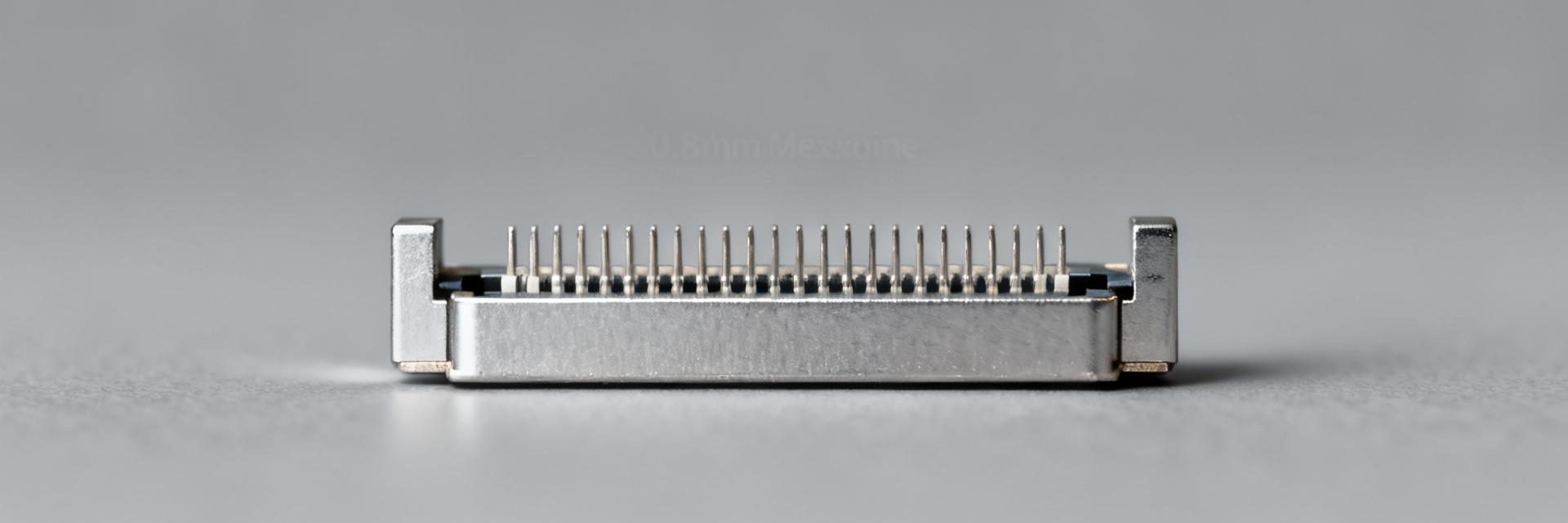

In-system programming and configuration wiring

Point: In-system programming requires specific pull resistors and header accessibility. Evidence: Configuration pins typically need pull-ups/pull-downs to set the device into the desired mode and a standard JTAG or ISP header for programming. Explanation: Add recommended pull resistors to nCONFIG/DONE lines, avoid directly tying configuration pins to noisy nets, and provide a removable programming header or solder jumper to allow firmware updates without disturbing the main connectors.

Example reference design & troubleshooting checklist (case + action)

Minimal reference design (schematic callouts & BOM highlights)

Point: A minimal working schematic centers on stable power, a clock source, and configuration elements. Evidence: Reference schematics typically show VCC with decoupling, a 10–100 kΩ pull on nCONFIG, a crystal or oscillator, and a JTAG header. Explanation: Include decoupling caps (0.1 μF and 10 μF), pull resistors (47 kΩ typical for config lines unless specified), a standard 10-pin ISP header footprint, and labeled test points for power rails and clocks for quick bench verification.

Common faults & troubleshooting flow

Point: A short prioritized troubleshooting list accelerates fault isolation. Evidence: Common failures are missing power rails, wrong pull states, or no clock present at startup. Explanation: Verify VCC and GND first with a multimeter, confirm decoupling integrity and absence of shorts, check config pin logic levels, probe for clock activity with a scope, and confirm programming connectivity with boundary-scan or a programmer utility.

Summary (conclusion)

- The ISPLSI 2096A delivers ~96 macrocells and ~96 I/Os suitable for mid-density CPLD roles; confirm package choice against pin and thermal needs and consult the official datasheet for absolute limits.

- Key pinout essentials include clustered VCC/VCCO pins, dedicated configuration signals, and JTAG lines; wire power rails first, add decoupling near pins, and mark pin‑1 on the silkscreen.

- Power sequencing and decoupling are critical; use 0.1 μF bypass caps at each VCC, a bulk cap on the rail, and validate timing margins via bench measurements before production.

FAQ

What are the key pin groups on the ISPLSI 2096A?

The device organizes pins into power (VCC, VCCO), ground (VSS/GND), I/O banks, configuration control pins (nCONFIG, nSTATUS/DONE), and programming/JTAG signals. Designers should identify which I/O banks are tied to each VCCO and avoid mixing incompatible voltage domains without level translation.

What supply voltage and decoupling are recommended?

Operate the device from the nominal 5 V domain (typical 4.75–5.25 V) and use local decoupling: 0.1 μF ceramic caps close to each VCC pin plus a 4.7–10 μF bulk capacitor on the rail. Follow power sequencing notes in the official datasheet to prevent configuration errors.

How do I wire the device for in-system programming?

Provide a standard ISP/JTAG header near the device, add recommended pull resistors on configuration pins to set boot mode, ensure the programmer can access nCONFIG and TCK/TMS/TDI/TDO lines, and include a removable header or solder jumper to allow field programming without PCB modification.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP