-

- Contact Us

F28F010-90 Datasheet Breakdown: Key Specs & Pinout

The F28F010-90 is a 1 Mbit (128K x 8) parallel flash device with a typical fast-read access of 90 ns. This practical datasheet breakdown extracts the numbers, pinout, timing and design guidance engineers need to integrate the device into legacy and low-cost embedded systems. The introduction highlights top-line specs, package pin mapping and the wiring cautions that minimize integration risk.

This article draws on hands-on integration experience and datasheet figures to present copy-ready spec bullets, a clear pin mapping table, timing translations and a compact checklist engineers can use during layout and firmware bring-up. The goal is actionable guidance—what to obey as absolute limits and what is typical behavior to expect in the lab.

Background: Device Overview & Key Specs (background introduction)

Key specs at a glance

Density and organization: 1 Mbit = 128K x 8. Nominal supply: 5 V family. Typical fast-read access: 90 ns (tACC). Typical program/erase cycles and data retention are specified in the official device documentation; endurance is in the 10^4–10^5 cycle region for standard parts, with retention guaranteed for years under recommended storage conditions. This H3 lists the essential top-line numbers engineers copy into spec sheets for quick design decisions.

Typical use cases & why it still matters

The device is useful for firmware storage on legacy MCUs, boot ROMs, and small-scale embedded logging where low cost and simple parallel interface trump density or serial bandwidth. Compatibility concerns include address-bus width, 8-bit parallel timing and 5 V signaling. Migration flags: parallel-to-serial bridging, voltage level translation and rework to accommodate larger linear address spaces in modern MCUs.

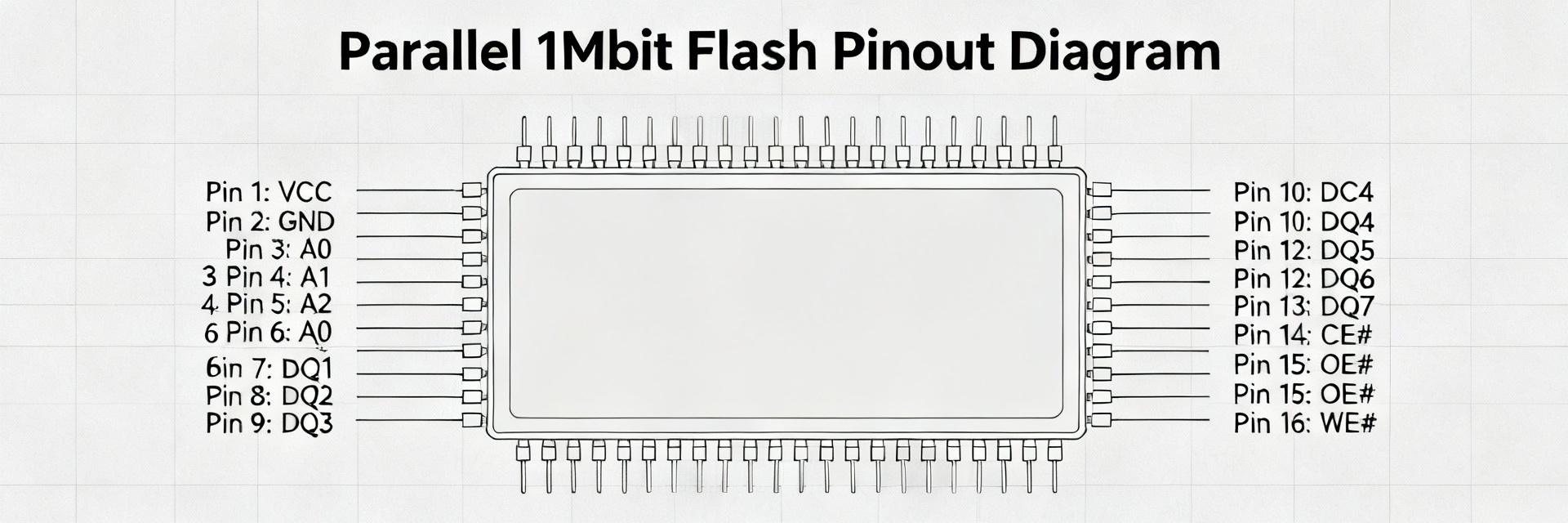

Pinout & Package Details (pinout)

Pin mapping for common packages (32‑pin DIP/PLCC/TSOP)

Below is a concise pin-number → signal mapping for the common 32-pin DIP variant. Address lines run A0–A16 (some high address pins multiplexed in package variants), data lines DQ0–DQ7, and control signals include /CE, /OE, /WE, VCC, GND and VPP/NC as applicable. Mechanical notes: TSOP variants require careful footprint control for solder fillet and coplanarity; DIP variants need stable socketing and lead cleanup before PCB insertion.

| Pin | Signal |

|---|---|

| 1 | A16 |

| 2 | A15 |

| 3 | A14 |

| 4 | A13 |

| 5 | A12 |

| 6 | A11 |

| 7 | A10 |

| 8 | A9 |

| 9 | A8 |

| 10 | A7 |

| 11 | A6 |

| 12 | A5 |

| 13 | A4 |

| 14 | A3 |

| 15 | A2 |

| 16 | A1 |

| 17 | A0 |

| 18 | DQ0 |

| 19 | DQ1 |

| 20 | DQ2 |

| 21 | DQ3 |

| 22 | DQ4 |

| 23 | DQ5 |

| 24 | DQ6 |

| 25 | DQ7 |

| 26 | /OE# |

| 27 | /WE# |

| 28 | /CE# |

| 29 | VPP or NC |

| 30 | GND |

| 31 | VCC |

| 32 | NC or manufacturer reserved |

Pin descriptions & practical wiring notes

Power pins: VCC should be decoupled with a 0.1 μF ceramic close to the package and a 10 μF bulk nearby; VCC pins must have short, low-impedance return paths to GND. Address pins: treat as static-driven during reads; avoid floating high-order address lines. Data pins: use series resistors (22–47 Ω) to damp reflections on long runs. Control pins: assert /CE, /OE and /WE to defined inactive levels via pull-ups/pull-downs to avoid accidental writes during reset or bus contention.

Electrical Characteristics & Timing Analysis (data analysis)

Absolute ratings & recommended operating conditions

Absolute maximums include supply over/under-voltage limits and input clamp thresholds—exceeding these risks permanent damage. Recommended operating VCC range centers on nominal 5 V ± tolerance; input voltages should never exceed VCC + 0.5 V or fall below GND −0.5 V. Static currents vary by device state; read and standby currents are typical and specified separately. Endurance and retention figures must be respected: program/erase cycles are finite and data-retention guarantees presume proper operating and storage conditions.

AC timing: read, program and erase timings explained

tACC (90 ns) defines the typical address-to-data valid time for a fast read; for N sequential reads from random addresses, throughput ≈ 1/(tACC + bus overhead). Example: reading 256 bytes sequentially at 90 ns per access yields a raw latency floor of ≈23 ms, excluding bus arbitration. Programming and block-erase times are orders of magnitude larger—milliseconds to seconds—so firmware must implement status polling with timeouts and retry logic to avoid infinite waits.

Programming, Erase & Protection (method guide)

Programming & erase sequences (practical steps)

Typical flow: 1) Issue command sequence to enter program mode; 2) present address and data; 3) pulse /WE per timing; 4) poll status register until complete; 5) verify by read-back. Use timeouts slightly above the maximum guaranteed program or erase time. Example pseudocode: write_page(addr,data); start_timer(max_program_ms); while (!status.done && !timer.expired) poll_status(); if (!status.done) flag_error(); verify_read(addr,data);

Sector protection & data integrity strategies

Protect critical regions using hardware write-protect pins where available and software locking protocols. Use CRC or small ECC for firmware images and a two-bank update strategy with bootloader fallback to prevent bricking. Implement watchdog-triggered rollback and conservative timeout values during in-field updates. Track erase/program cycle counts per block to schedule preemptive replacements in long-lived deployments.

Practical Design Checklist & Troubleshooting (action advice)

Integration checklist (power, layout, interface)

Copy this checklist into design reviews: 1) Place 0.1 μF decoupling within 2 mm of VCC pin and 10 μF bulk on board; 2) Keep address and data traces grouped and matched in length where possible; 3) Route control signals away from noisy clocks; 4) Provide testpoints on VCC, /CE, /OE, /WE and DQ0–DQ7; 5) Add series dampers on long DQ lines and level-shifters if mixing voltages.

Common failure modes & debugging tips

Typical failures: incorrect pin wiring, missing decoupling, bus contention, timing violations and improper VPP handling. Quick triage: check VCC/GND with scope, confirm idle levels on /CE/ /OE/ /WE, isolate the flash from the bus and perform single-word program/verify cycles. Use a logic analyzer to capture command sequences and confirm timing margins against the timing checklist above.

Summary

- The F28F010-90 is a 1 Mbit (128K x 8) parallel flash with 90 ns typical read and 5 V signaling; integrate using the pinout mapping and obey absolute operating limits for reliability.

- Follow the wiring and layout checklist: tight decoupling, grouped address/data routing, series resistors on DQ lines and defined pull states for control pins to prevent accidental writes.

- Implement robust firmware procedures: status polling with timeouts, verify-after-write, CRC/ECC and dual-bank update patterns to avoid bricking during in-field updates.

Frequently Asked Questions

How should engineers verify program and erase operations?

Engineers should poll the device status register after issuing program or erase commands, implement a conservative timeout slightly above the maximum guaranteed operation time, and perform a full read-back verification of the programmed region. Keep error counters and fallback recovery paths to handle intermittent failures.

What wiring practices prevent bus contention on a parallel flash interface?

Ensure each bus master releases data lines when not driving, use pull-ups or pull-downs to define inactive levels, and include series resistors on DQ lines for damping. During bring-up, isolate the flash and validate single-master control to eliminate contention before adding other bus agents.

Which testpoints and measurements speed debugging during bring-up?

Place accessible testpoints on VCC, GND, /CE, /OE, /WE and representative DQ lines. Measure supply stability under load, capture command sequences with a logic analyzer, and use a scope to confirm timing and signal integrity. A defined pattern test (write/read/verify) is the fastest functional verification.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP