-

- Contact Us

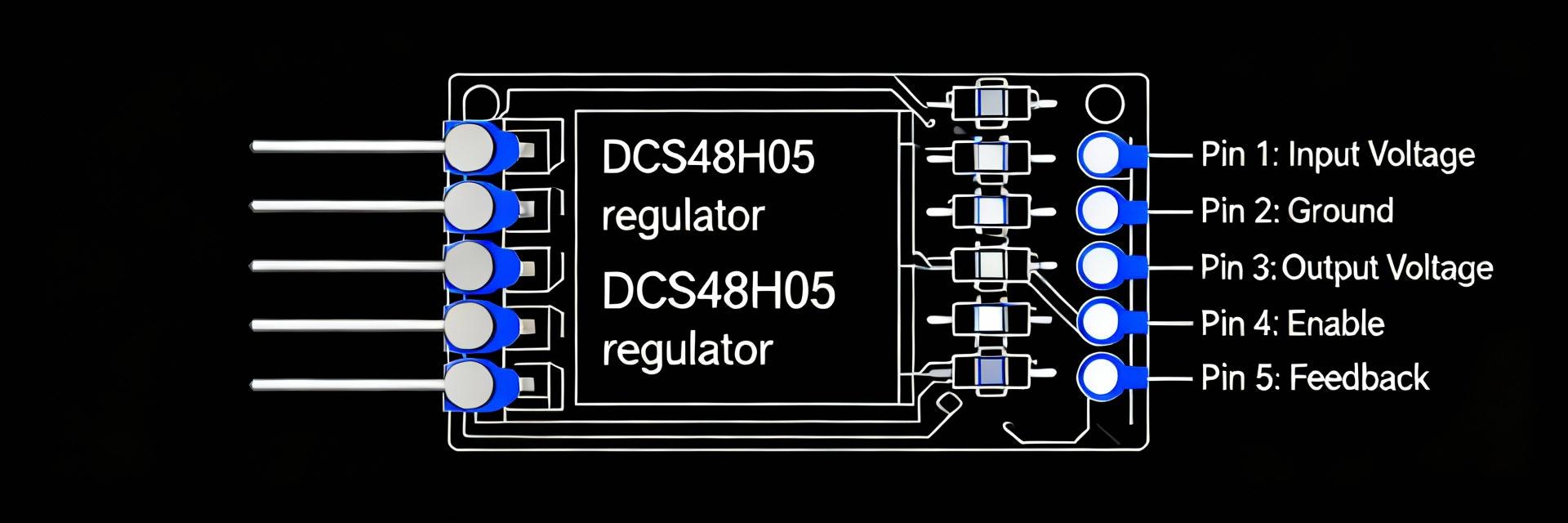

DCS48H05 Pinout & Specs: How to Read the Datasheet Fast

Fed up with hunting a long datasheet for a single deciding spec? This concise guide shows a step-by-step, time-saving approach so an engineer can extract the DCS48H05 datasheet essentials and the DCS48H05 pinout in minutes, then move directly to schematic, layout, and test with confidence.

1 — Quick background: What the DCS48H05 is and where it’s used (Background introduction)

1.1 Key device summary and common applications

The DCS48H05 is a switching regulator module class typically used to generate isolated or non‑isolated 5 V rails from higher‑voltage sources; it’s offered across compact power packages for board‑level integration. Common uses include microcontroller power rails, bench‑power subsections, and industrial control modules. Mental model bullets: 1) regulator module converting higher bus voltages to a regulated 5 V rail; 2) target for low‑noise decoupling, thermal management, and sensing.

1.2 At-a-glance spec snapshot (table)

| Parameter | Typical Entry (verify on datasheet) |

|---|---|

| Input voltage range | Wide: ~4.5–60 V |

| Output voltage(s) | Fixed 5 V (variants adjustable) |

| Max current | Up to 5 A (package dependent) |

| Efficiency | Up to 90–95% at moderate load |

| Thermal rating | RθJA typical 20–40 °C/W, Tj max ~150 °C |

| Package | QFN / power SOIC / through‑hole options |

When scanning, verify input range, max current, and thermal rating first: if any of those three mismatch your system requirements, stop and choose another part. The table is a condensed checklist — always cross‑check exact numbers and test conditions on the official page.

2 — Pinout overview: reading the pin map fast (Data-analysis)

2.1 Pin-by-pin breakdown: power pins, grounds, signals, and NC

Open the package drawing and the pin table together: label VIN, VOUT, multiple GNDs, sense pins, enable/shutdown, and NC. Quick checks: mark VOUT pins for high‑current routing and decoupling, mark exposed thermal pad as ground/copper tie, and note any sense or remote‑sense pins that require Kelvin routing. A short checklist: mark power pins, mark grounds, identify NC and signal pins, and flag thermal pads for via stitching.

2.2 Package & footprint considerations

Pay attention to package variant and the recommended land pattern: pads for a QFN thermal pad require solder‑mask defined openings and a specific via count. When preparing the PCB, follow the vendor’s copper pour recommendations, add thermal vias under the pad (commonly 6–12 depending on current and board layers), and respect keepouts for reflow. For a quick search, include a DCS48H05 pinout reference to verify pad names match your schematic symbols before footprint release.

3 — Rapid-datasheet method: a 5-minute checklist to find critical specs (Method/How-to)

3.1 Priority order: sections to read first and why

Five‑minute scan order: 1) Absolute maximum ratings — these are the kill‑switch numbers; 2) Electrical characteristics — operating voltages, currents, ripple; 3) Thermal data and derating curves — board thermal budget; 4) Pin descriptions and package drawings — footprint and routing. Template: “Scan the absolute max page → electrical characteristics table → thermal/derating figures → pin map/page with package drawing.”

3.2 Quick calculations and units sanity checks

Do fast sanity math: headroom and dissipation. Example: Pd = (Vin – Vout) × Iout for a linear pass or for worst‑case switching losses add (1‑efficiency)×(Vin×Iout) for switching converters. Check units and test conditions (Ta vs Tc). Red flags include unspecified test conditions, missing RθJA, or efficiency quoted only at low loads; those require deeper scrutiny before committing to layout.

4 — Interpreting the key specs: what they mean for design & testing (Data + Method)

4.1 Electrical specs explained: Vins, Vouts, efficiency, switching limits

Differentiate typical versus guaranteed columns and note test conditions (Ta, Tc, fixed input). Efficiency and switching frequency translate directly into heat and EMI: higher switching frequency may reduce external inductance size but increases EMI and switching losses. Record VIN/VOUT tolerances, max ripple, and switching frequency in component selection notes for simulator and layout decisions.

4.2 Thermal, reliability, and protection features

Use RθJA and RθJC to budget PCB heat: ΔT = Pd × RθJA gives ambient rise; combine with derating curves to find permissible continuous current at your board environment. Identify protections like OVP, OCP, and OTP and how they report (latched vs auto‑recover). Note any junction temperature limits or MTBF hints to decide on heatsinking, derating, and test stress levels.

5 — Practical workflow & examples: from datasheet to schematic and board (Case + Action)

5.1 Real-world selection & schematic integration (mini walkthrough)

Example: need 5 V @ 2 A. Extract from the electrical table the guaranteed VOUT tolerance at 2 A, efficiency at that current, and ripple spec. From thermal data compute Pd and determine required thermal vias. Capture required passives from the application table — decoupling capacitor values, output filter components, and any recommended sense resistor or footprint notes — then translate those into schematic BOM entries and net labels.

5.2 Test checklist & PCB layout tips to avoid re-spins

Pre‑layout: ensure thermal pad, sufficient copper, star ground for returns, and wide traces for high‑current nets. Post‑pop: use a current‑limited bench supply for first power‑up, probe output with the scope at the load‑side decoupling cap, and measure ripple and switching node with proper probe grounding. If results deviate, recheck probe placement, board thermal coupling, and actual VIN under load versus expected.

Summary

- Use a pinout‑first scan to mark VIN, VOUT, grounds and the thermal pad, ensuring physical nets match schematic labels before layout begins; this reduces footprint mistakes and rework.

- Apply the 5‑minute checklist: absolute max → electrical → thermal → pin map; record Pd = (Vin–Vout)×Iout and compare against RθJA derating to validate cooling.

- Keep a concise component note: required decoupling, sense resistor, and layout callouts; confirm the DCS48H05 datasheet numbers against board assumptions before committing to prototypes.

Frequently Asked Questions

How quickly can an engineer find the DCS48H05 pinout in the datasheet?

With the five‑minute method, an engineer can locate the pin map immediately by jumping to the package drawing and pin description sections—typically within the first two pages of mechanical data. Mark power, ground, and thermal pads on a printed copy to speed footprint verification before layout.

What are the top thermal checks to do from the DCS48H05 datasheet?

Extract RθJA/RθJC, the junction temperature limit, and any derating curves. Use Pd × RθJA to estimate ambient rise; if the resulting Tj approaches the max junction temperature, add thermal vias, copper pours, or a heatsink. Verify test conditions in the datasheet to match your board environment.

Which measurements should be first on the bench when validating a board with the DCS48H05?

Begin with a current‑limited supply, measure no‑load and full‑load voltages at the output decoupling capacitor, then capture ripple at the output and the switching node with the scope. Confirm thermal behavior under load and watch for protections (OCP/OTP) before extended testing.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP