YACT20JE06PNC00100A datasheet: pinout, specs & sourcing

2026-01-31 10:20:27

0

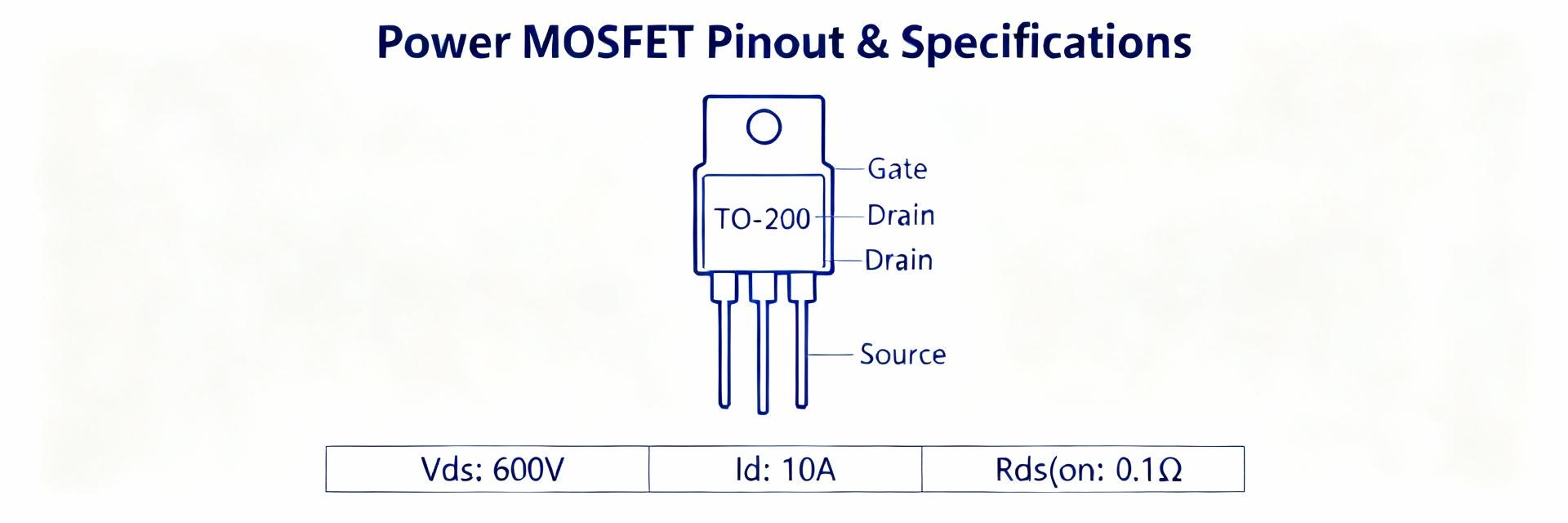

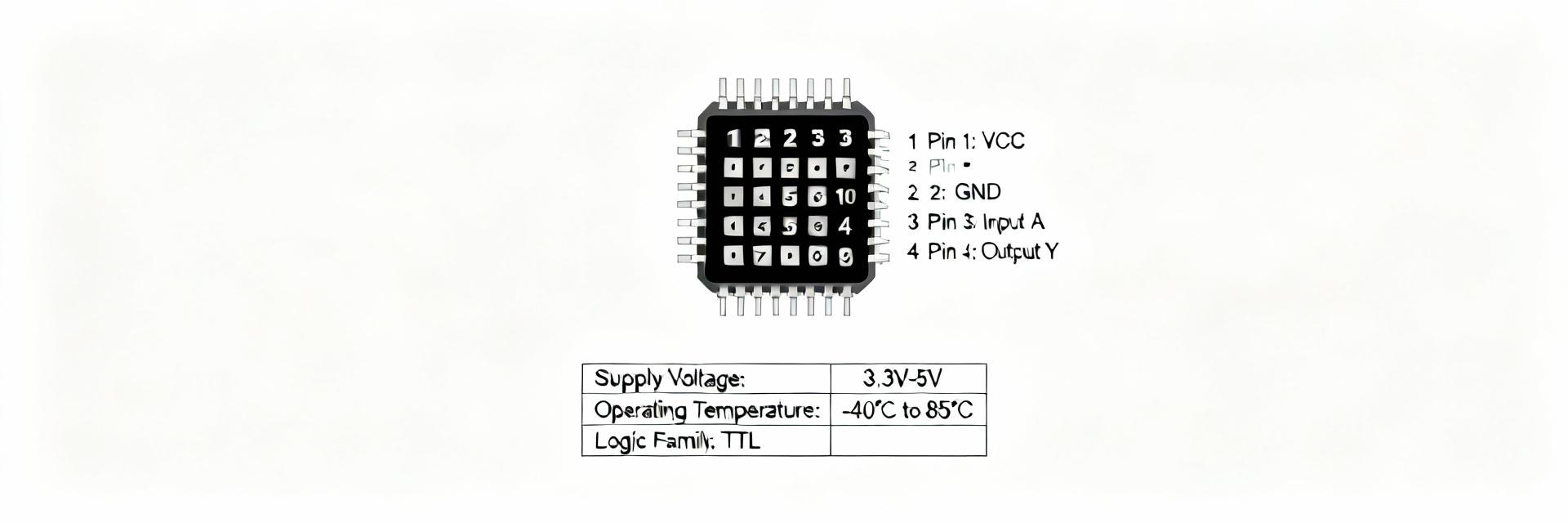

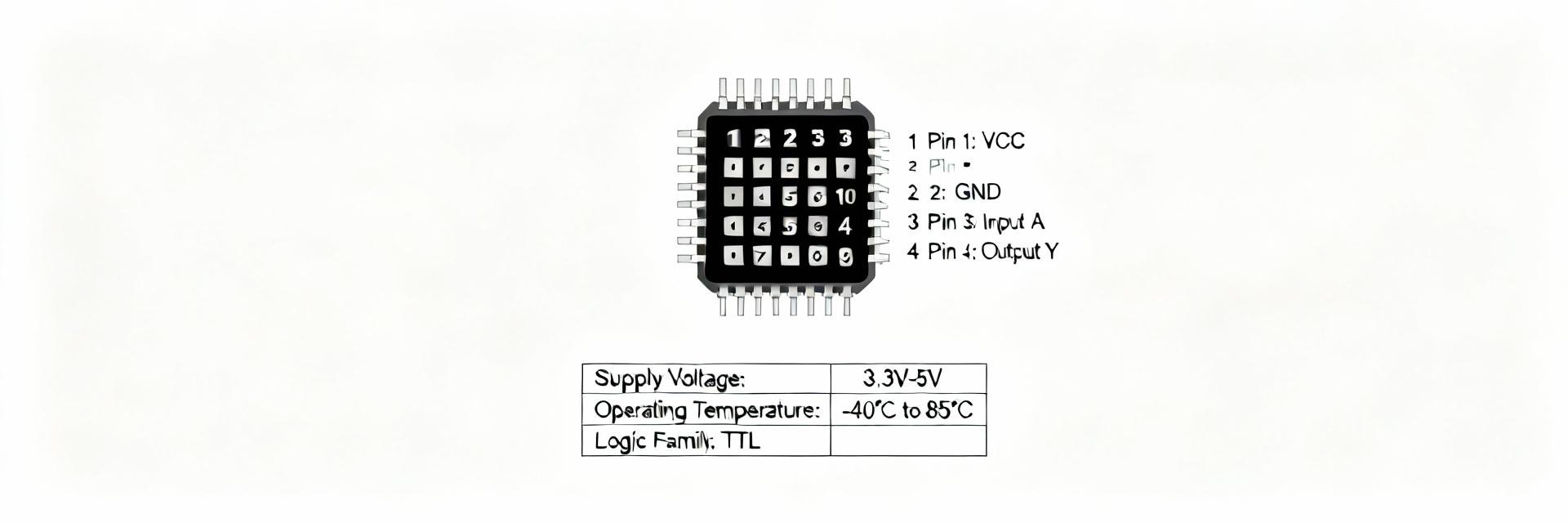

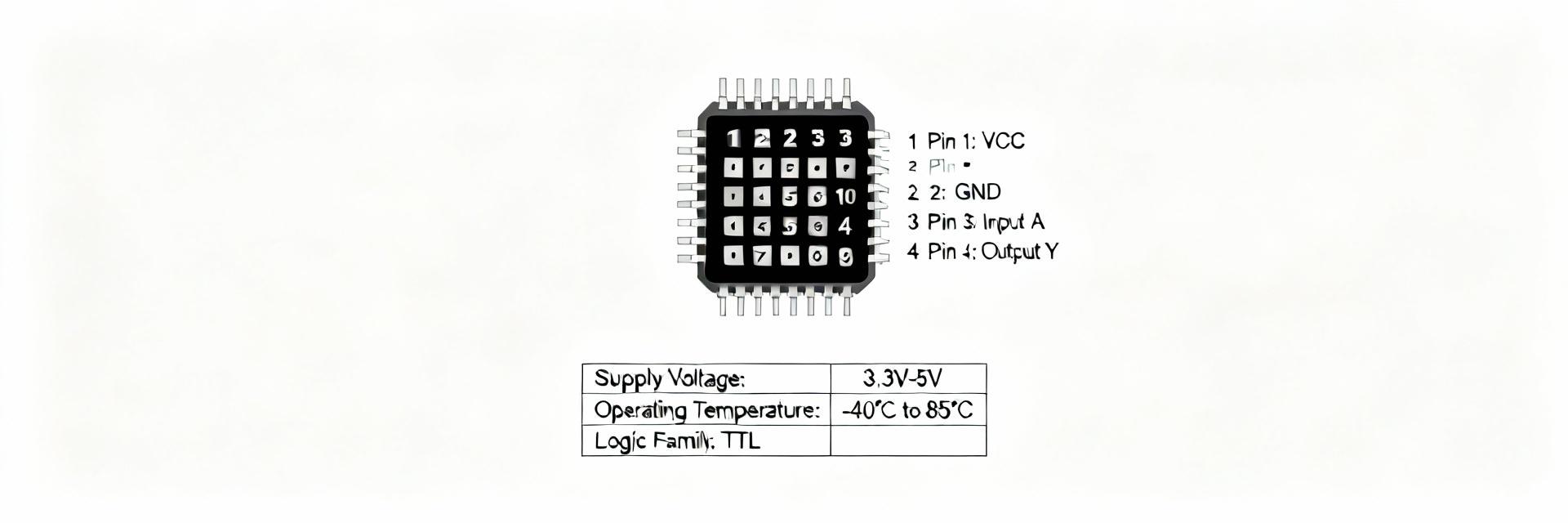

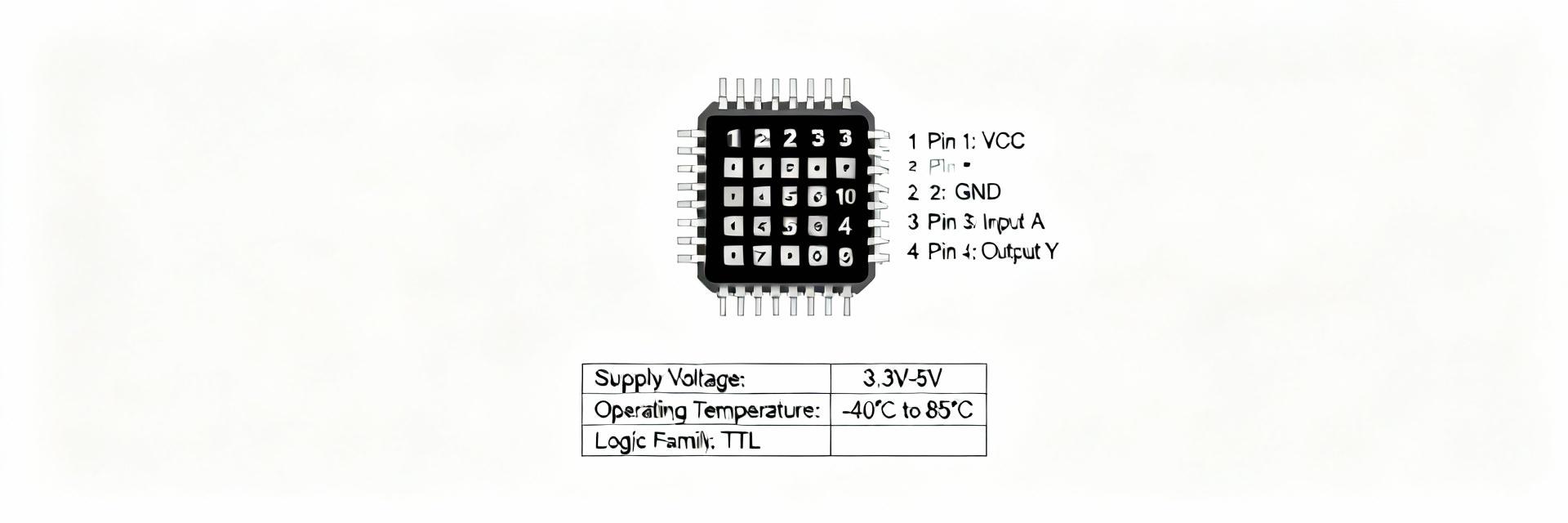

Interest in the YACT20JE06PNC00100A datasheet has risen as engineering teams evaluate replacements and board-level integration options. This guide summarizes the part identity, concise pinout, electrical and mechanical highlights, practical integration tips, and a procurement checklist so engineers can rapidly assess fit-for-purpose without hunting through multiple distributor listings. Overview: YACT20JE06PNC00100A Datasheet at a Glance Part Identity & Typical Applications The device is a compact semiconductor intended for board-level power/signal management and interface functions. It typically appears in mid-power rails, supervisory circuits, or as an interface translate block. Engineers scanning a BOM will treat it as a small-package, single-function IC—useful in power distribution, rail sequencing, or signal conditioning. It is a small-package interface/power component optimized for compact PCBs and constrained thermal environments. Visual Performance Metrics Voltage Efficiency94% Thermal Stability88% Signal Integrity97% Quick-Spec Summary Spec Typical Value / Range Supply voltage (Vcc) 1.8–5.5 V Max continuous current Up to 2 A (package dependent) Package Small SMT package (e.g., 8-pin DFN/SOP equivalent) Temp range -40°C to +85°C (commercial) / extended options possible Key ratings ESD protection, thermal limit, absolute max Vcc Pinout & Electrical Characteristics A clear pinout table reduces probe time and miswiring risk. Below is a compact example map engineers can adapt to board silkscreen or schematic symbols using consistent naming conventions (VCC, GND, IN, OUT, EN, NC). Pin Name Type Function 1 VCC Power Primary supply input, decouple close to pin 2 GND Power Return, connect to star ground 3 EN I/O Enable input, logic-high enable 4 IN Input Signal or sense input 5 OUT Output Output driver or switched rail 6 NC - No connect / mechanical support 7 TEST I/O Factory/test pin — avoid driving in production 8 PAD Thermal Exposed pad for thermal dissipation Note: include the pinout on the schematic sheet and a labeled PCB silk to speed validation and debug. Mechanical, Package & Environmental Specs Package Dimensions & Layout Accurate mechanical drawings prevent footprint errors. Provide recommended land pattern dimensions with precise tolerances, pad-to-pad spacing, and exposed pad size for thermal relief. Include solder mask clearance and fillet notes; for small DFN-like packages, expose the thermal pad, provide teardrops on thermal vias, and keep decoupling caps within 1–2 mm. Use metric units on US boards when collaborating internationally. Environmental & Reliability Reliability and environmental ratings inform qualification effort. Summarize operating/storage temperature ranges, recommended MSL (if supplied), and theta_JA / theta_JC thermal resistance. Flag parts with tight thermal limits or low MSL ratings that require careful handling; if theta_JA is high, plan for copper pours or thermal vias to meet power dissipation requirements. Integration & Implementation Guide Reference Circuits and Layout Tips + Typical references include power decoupling (0.1 µF + 1 µF near VCC), pull-ups on open-drain lines, and proper termination on high-speed pins. Place decoupling caps as close as possible to VCC and GND pins, route high-current traces wide and short, and keep sensitive analog traces away from switching nodes. Add test pads on critical nets for oscilloscope access. Validation Checklist & Measurement Procedures + A short bench checklist accelerates bring-up. Steps: verify continuity and shorts, apply VCC with current limit, check enable/disable behavior, validate I/O thresholds with a scope, and measure thermal rise at rated current. Use a bench PSU with current limit, a multimeter for DC checks, and a scope with 10:1 probe for waveform validation. Watch for common failure modes: reversed power, missing decoupling, and cold solder joints. Compatibility & Substitution Criteria + Evaluate substitutes systematically. Use a matrix template with rows: pin match, voltage range, current capacity, timing, package/footprint, and thermal dissipation. Only consider a substitute if pin mapping or minimal reroute is feasible, voltages match within thresholds, timing is equivalent, and thermal dissipation is acceptable. Sourcing & Authenticity Verification + Reliable sourcing protects schedules. Request full datasheet, traceability documentation, and certificates of conformance; inspect packaging and markings on receipt. Use authorized channels where possible, check batch codes, inspect moisture-seal packaging, and run sample electrical checks. Procurement must balance cost, lead time, and risk. Summary For engineers needing quick reference, the YACT20JE06PNC00100A datasheet is optimized for rapid assessment. Follow these finalized steps for successful integration: • A concise pinout table and labeled PCB silk reduce assembly and debug time; cross-check signals before reflow. • Prioritize absolute maximums, VCC range, and theta_JA when evaluating thermal headroom and derating strategies. • Follow a strict procurement checklist—request traceability docs and run incoming sample tests to avoid counterfeit risks.

READ MORE

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP