-

- Contact Us

YACT20JE06PNC00100A Datasheet Deep Dive: Key Specs & Pinout

An essential engineering guide for rapid power design assessment and implementation.

This deep dive extracts the critical figures engineers need from the device datasheet so you can judge suitability for power designs in minutes. It focuses on voltage/current limits, RDS(on), switching characteristics, thermal ratings, and the full pinout—helping you quickly locate, interpret, and apply those values during schematic and PCB work.

Purpose: Enable fast decisions—identify headline specs, run quick conduction and switching loss checks, and place the device correctly in layout based on datasheet tables and mechanical drawings.

Part Overview & Key Specs at a Glance

Functional Description

This device is a power MOSFET intended for switching applications. Classified as a low-RDS(on) switching transistor, it features optimized gate thresholds and charge. It is ideal for synchronous buck stages, motor drivers, and high-speed switches where low conduction loss and defined gate-drive energy are mandatory.

Application Target

Optimized for efficiency in power conversion. The electrical, switching, and thermal parameters are organized to facilitate initial feasibility checks and BOM (Bill of Materials) comparison during the design phase.

Key Parameter Dashboard

| Parameter | Typical / Specification | Datasheet Location |

|---|---|---|

| VDS (max) | 60 V | Absolute Ratings Table |

| ID (continuous) | 30–60 A | DC Characteristics Table |

| Pulsed Current | Peak Pulse as specified | Absolute Ratings / Pulse Ratings |

| RDS(on) | Typ/Max @ 10V VGS | On-state Resistance Table |

| Total Gate Charge (Qg) | 40–80 nC | Switching Characteristics |

| Package / Thermal | θJA / θJC | Mechanical / Thermal Info |

Electrical Characteristics: DC & Switching Parameters

DC Parameters

Prioritize RDS(on), Vth, ID rating, and leakage. Use worst-case RDS(on) at elevated temperatures for conduction loss estimates. The datasheet typically provides a temp coefficient to scale resistance from 25°C to the operating Tj.

AC / Switching Specs

Gate charge (Qg) and capacitances (Ciss) define gate-driver needs.

Psw ≈ 0.5 × VDS × ID × (tr+tf) × f

Example: VDS=48V, ID=20A, tr+tf=50ns, f=200kHz → Psw ≈ 0.48 W.

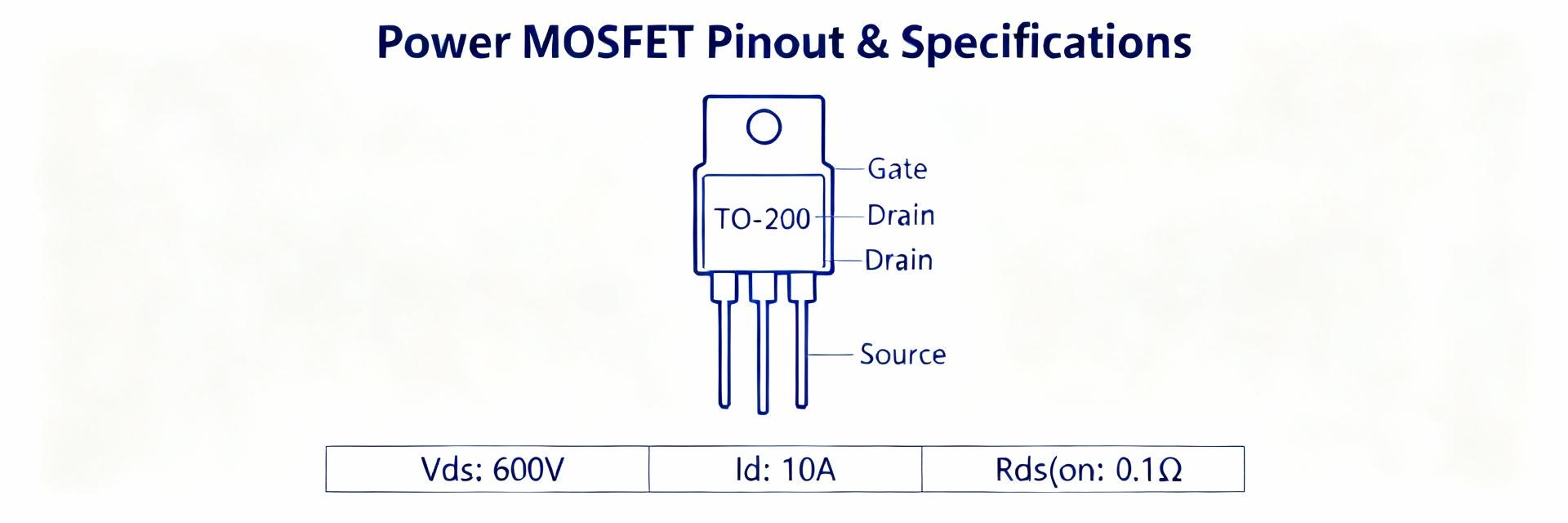

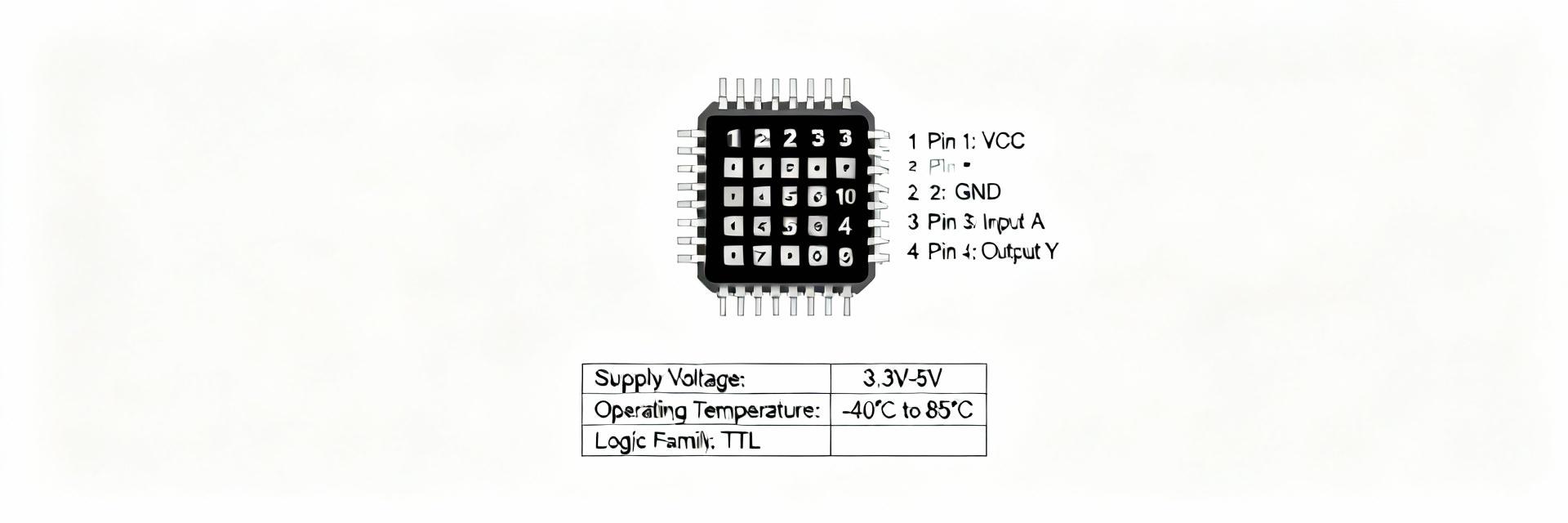

Pinout, Package, and Mechanical Details

- Gate (G): High-impedance control

- Drain (D): Main current input/case

- Source (S): Current return path

- Exposed Pad: Thermal & Ground

Layout Guidance: Implement thermal vias under the exposed pad (8–20 moderately spaced vias) and increase copper pour to lower θJA. Follow the recommended land pattern precisely to ensure mechanical reliability and optimal solder fillets.

Thermal Performance & Safe Operating Area (SOA)

Safe Operating Area (SOA): Always cross-reference your V-I operating point with the SOA curves. For repetitive pulses, apply conservative derating—limit continuous current well below pulsed peaks. Verification: ΔTj = Pd × θJA. If Pd = 10 W and θJA = 30 °C/W → ΔTj = 300 °C (requires active cooling or more copper).

Application Example: Synchronous Buck Power Stage

Design check for ID=30 A and RDS(on)=20 mΩ:

- Place a gate resistor (10–50 Ω) to damp ringing.

- Include a bootstrap diode for high-side drive.

- Add a snubber circuit if dV/dt ringing exceeds 80% of VDS rating.

Testing & Validation Checklist

Bench Verification

- Measure RDS(on) using Kelvin 4-wire method.

- Capture switching waveforms with low-inductance probes.

- Perform thermal imaging under steady-state load.

PCB Layout

- Keep gate traces as short as possible.

- Decouple power rails directly at Drain/Source.

- Verify solder reflow profile compatibility.

Summary

- Electrical: Use VDS, ID, and RDS(on) tables to compute conduction and switching losses immediately.

- Thermal: Extract θJA/θJC to design copper area and via count, ensuring junction limits are never breached.

- Mechanical: Confirm pinout and footprint from the mechanical section for perfect board alignment and thermal pathing.

Frequently Asked Questions

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP