-

- Contact Us

TG110-AE050N5LF Datasheet: Compact Pulse Transformer Specs

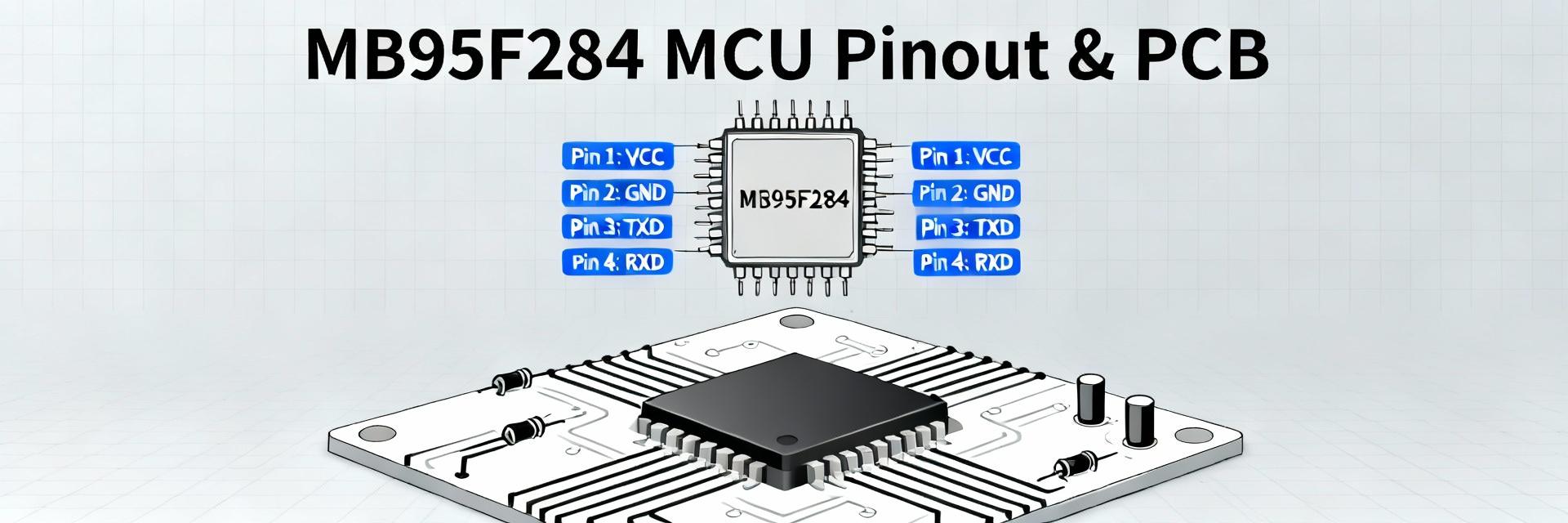

The TG110-AE050N5LF is a compact surface-mount pulse transformer optimized for constrained board designs that require robust isolation and reliable coupling. Key datasheet figures include rated inductance ≈350 µH, isolation ≈1.5 kV, operating range −40 to +85 °C, DCR ≤0.9 Ω, inter-winding capacitance ≈35 pF, and a small SMD-16 package roughly 0.500" × 0.280" (12.7 × 7.11 mm). These headline numbers show why this part suits space- and cost-sensitive 10/100BASE-T implementations.

Purpose: this pulse transformer is intended for compact 10/100BASE-T magnetic coupling and telecom line isolation and coupling where a low-profile SMD solution with 1CT:1CT turns ratio and modest parasitics is required. The following sections extract datasheet values, explain design impact, and give bench and PCB guidance for an engineer integrating this pulse transformer into production designs.

TG110-AE050N5LF at a glance — product overview (Background introduction)

What this pulse transformer is

Point: The device is a surface-mount pulse transformer for Ethernet and telecom interfaces, built around a center-tapped 1CT:1CT winding topology to support balanced signal coupling and common‑mode rejection. Evidence: Datasheet headline specs show inductance around 350 µH and isolation near 1.5 kV, with DCR under roughly 0.9 Ω and inter-winding capacitance near 35 pF. Explanation: That combination gives enough magnetics impedance at low frequency for 10/100 Mbps while keeping leakage and capacitance low enough to manage common‑mode noise and return‑loss.

Typical target applications

Key electrical specifications from the datasheet (Data analysis)

Core electrical numbers to extract and explain

Point: Extracted core numbers—inductance ≈350 µH, turns ratio 1CT:1CT, DCR ≤0.9 Ω, inter‑winding capacitance ≈35 pF, isolation ≈1.5 kV—drive signal integrity and safety margins. Evidence: These are the datasheet's characteristic entries used in margin calculations for rise time, insertion loss, and isolation testing. Explanation: Higher inductance improves low-frequency coupling; low DCR minimizes DC and I2R losses; low capacitance reduces common‑mode feedthrough and EMI; adequate isolation supports hi‑pot testing and safety compliance.

| Specification | Typical Value | Design Impact |

|---|---|---|

| Inductance | ≈350 µH | Ensures sufficient low‑frequency coupling for 10/100 Mbps; affects low‑end bandwidth and rise time. |

| DCR | ≤0.9 Ω | Lower losses, less heating; helps preserve signal amplitude and reduces common‑mode dissipation. |

| Inter‑winding C | ≈35 pF | Affects common‑mode feedthrough, EMI and return loss at higher frequencies. |

| Isolation | ≈1.5 kV | Defines hi‑pot test margin and safety separation for telecom or automotive requirements. |

How to read the datasheet values and tolerance implications

Point: Datasheet entries include typical and maximum/minimum columns; treating typical as nominal and maximums as design limits is critical. Evidence: Inductance tolerances, DCR ranges, and capacitance variance across temperature directly change performance. Explanation: Use worst‑case values (e.g., minimum inductance, maximum DCR, maximum capacitance) when deriving insertion loss, thermal rise, and hi‑pot margin; factor temperature coefficients and add safety margins (commonly 20–30%) during margin calculations.

Frequency response, parasitics and real-world performance (Data analysis)

Frequency response & insertion loss expectations

Point: For 10/100 Mbps, the transformer must pass rise times and baseband spectra with minimal attenuation. Evidence: Datasheet frequency plots—when present—show insertion loss/bandwidth; absent plots, designers rely on inductance, parasitics and empirical bench data. Explanation: Expect adequate low‑frequency impedance from 350 µH to support 10/100BASE‑T; verify insertion loss with a network analyzer across the 1 kHz–100 MHz band to confirm rise‑time preservation and minimal amplitude loss at fundamental frequencies.

Parasitics: capacitance, leakage, and effect on EMI/return loss

Point: Inter‑winding capacitance and leakage inductance determine common‑mode feedthrough and return loss. Evidence: ~35 pF inter‑winding capacitance passes high‑frequency common‑mode components, which can degrade EMI and return loss if not filtered. Explanation: Use common‑mode chokes and placement strategies to mitigate; bench tests—LCR meter for capacitance, impedance analyzer for frequency response—should confirm datasheet parasitics and help size any supplementary filtering.

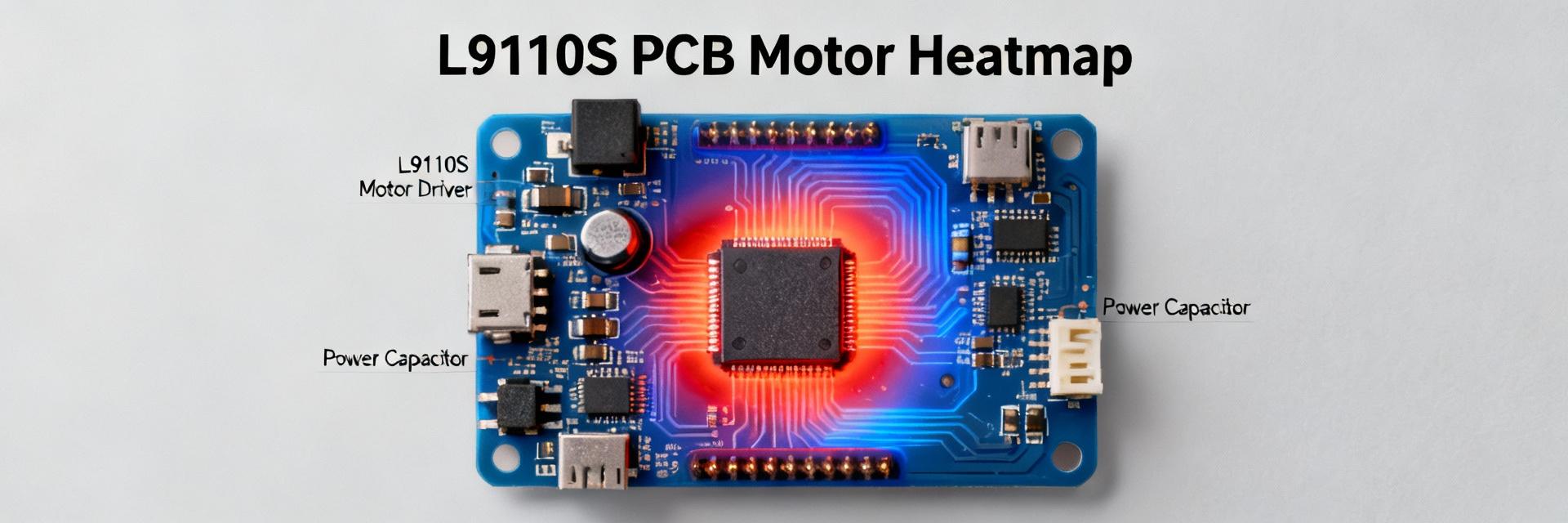

PCB integration and mechanical / thermal guidance (Method guide)

Footprint, soldering, and land pattern best practices

Point: Proper footprint and placement influence performance and solder reliability. Evidence: The SMD‑16 package (≈12.7 × 7.11 mm) requires adequate solder fillet clearance and controlled pad geometry. Explanation: Keep primary and secondary return paths short and symmetric, minimize loop area between PHY and transformer, maintain recommended pad-to-pad spacing for isolation, and follow an industry standard land pattern with thermal reliefs to ensure consistent reflow and wetting.

Thermal considerations and reliability (reflow, temperature range)

Point: Reflow profile and ambient derating affect long‑term reliability. Evidence: Operating range rated to −40 to +85 °C implies automotive-style robustness; DCR and losses increase with temperature. Explanation: Use standard Pb‑free reflow profiles, avoid overheating during assembly; apply copper pour to aid thermal dissipation but avoid creating large heatsink areas that alter solder fillets. Perform thermal cycling to verify mechanical stress limits for SMD mounting.

Application examples and selection checklist (Case showcase + Method)

Example: 10/100BASE‑T magnetic coupling implementation

Point: Integrating the part for Ethernet requires verification of turns ratio, isolation margin, and placement relative to the PHY and RJ45. Evidence: A typical implementation places the transformer between the PHY magnetics and the connector, with common‑mode choke where additional suppression is needed. Explanation: Verify 1CT:1CT ratio matches transformer wiring expectations, ensure isolation exceeds required hi‑pot margin, and place magnetics close to PHY to minimize stub length and preserve return paths.

Quick selection checklist (how to confirm fit)

Testing, verification, and compliance checks before production (Action recommendation)

Recommended bench and in-circuit tests

Point: Perform hi‑pot, DCR, insertion/return loss, and temperature cycling before production. Evidence: Datasheet limits guide pass/fail thresholds—e.g., DCR ≤0.9 Ω and isolation ≈1.5 kV—so derive margins from those values. Explanation: Use a hi‑pot tester with a safety margin (e.g., 1.5× rated), LCR for DCR and capacitance, and network analyzer for insertion/return loss; include temperature chamber cycling to reveal mechanical or parametric drift.

Compliance & automotive/industry considerations

Point: Confirm regulatory and automotive suitability where applicable. Evidence: Temperature range and isolation spec inform AEC-style suitability but do not substitute for formal qualification. Explanation: Ask for AEC/Q or equivalent qualification if automotive deployment is required; set incoming inspection for tape‑and‑reel handling and sample lot acceptance testing to catch packaging or solderability issues early.

Summary (10–15% of total words)

Additional SEO & writing instructions for the author

What must I check in the TG110-AE050N5LF datasheet before design commit?

How should I validate the pulse transformer in-circuit for target bandwidth?

Which tests are critical for qualifying TG110-AE050N5LF for automotive applications?

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP