-

- Contact Us

MAX483CSA: Datasheet Deep Dive — Specs, Pinout, Uses

Reliable multi-drop and long-haul serial links for industrial communication.

The MAX483CSA appears in this deep dive as a low-power, slew-rate-limited RS-485/RS-422 transceiver intended for reliable multi‑drop and long‑haul serial links. Key figures to keep in mind from the datasheet include typical class data rates around 250 kbps for stable multi‑drop operation and differential signaling that supports cable runs well into the thousands of feet with correct topology and termination. This article decodes the datasheet to extract practical specs, pinout guidance, timing interpretation, application circuits, and a hands‑on troubleshooting checklist for system integration.

Readers will find a concise product overview and an at‑a‑glance spec table, focused electrical and dynamic performance interpretation, explicit pin functions and PCB footprint advice, recommended application circuits for point‑to‑point and multi‑drop RS‑485 networks, and stepwise design and debug best practices. Primary terms used naturally include MAX483CSA, datasheet, and pinout to aid search relevance while keeping the content practical for US engineering teams.

1 — Product Overview & Key Features (Background)

What the MAX483CSA is and where it fits

The device is a single‑driver / single‑receiver RS‑485/RS‑422 transceiver optimized for low quiescent current and controlled driver edge rates to limit EMI. Typical targets are industrial communications, instrumentation, and medium‑to‑long distance serial links. Datasheet claims usually highlight a supply range suitable for 5V systems, low ICC in idle, slew‑rate limiting for EMI control, and compact surface‑mount packages. Designers should reference the MAX483CSA datasheet PDF key features when picking part variants and derating for temperature.

At-a-glance spec table

| Parameter | Notes to pull from datasheet |

|---|---|

| VCC range | Recommended vs absolute‑max (annotate typical value) |

| ICC (driver/receiver) | Typical quiescent and active currents |

| Max data rate | Typical 250 kbps class rating; absolute timing limits |

| Common‑mode range | Bus tolerance relative to GND |

| Driver output swing | Typical differential amplitude and loaded values |

| Receiver thresholds | Fail‑safe behavior and input thresholds |

| Thermal limits | Junction and ambient derating notes |

| Package type | Surface‑mount markings and lead count |

2 — Electrical Specifications & Performance Analysis (Data analysis)

Absolute maximums, supply and thermal limits

Interpreting absolute‑maximum ratings in the datasheet is vital: treat them as survival boundaries, not operational targets. Use the recommended operating conditions for design margins, place a 0.1µF decoupling cap close to VCC and GND, and calculate worst‑case power dissipation from ICC × VCC plus driver switching losses. For elevated ambient (e.g., 70°C) apply package thermal resistance to derive allowable continuous power and reduce duty or add airflow to maintain safe junction temperature.

Dynamic performance: slew rate, data rate, EMI, and receiver characteristics

Slew‑rate limiting trades fastest possible edges for reduced EMI and smaller ringing on long runs; the datasheet’s typical 250 kbps guidance is conservative for multi‑drop topologies. Read timing graphs to extract propagation delays, driver enable/disable times, and receiver habilitation; combine those numbers into a system timing budget for inter‑byte gaps and turnaround times. Pay attention to fail‑safe inputs, receiver hysteresis, and common‑mode range to ensure robust idle bus and noisy‑environment immunity.

3 — Pinout, Package & Timing Diagrams for MAX483CSA (Method/guide)

Pin functions and recommended PCB footprint

Typical pin names are DE (driver enable), RE (receiver enable, active low), DI (driver input), RO (receiver output), A, B (differential bus), VCC and GND. Place the 0.1µF decoupling capacitor as close as possible to VCC and GND pins, stitch ground vias near the device, and route the differential bus traces symmetrically with matched lengths. Include a clearly labeled pinout graphic in your layout notes and verify land pattern dimensions against the vendor’s mechanical drawing before PCB fab.

Timing diagrams, control signals and interface behavior

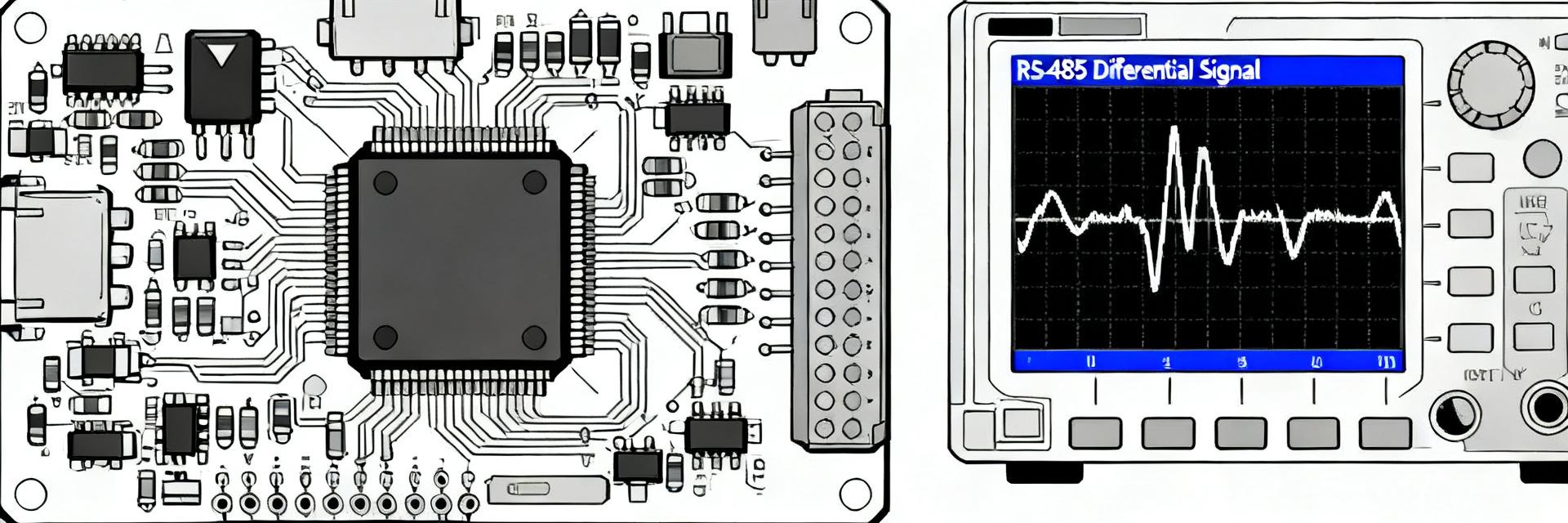

Use the datasheet timing diagrams to derive DE/RE sequencing: observe driver enable time, disable time, and receiver propagation delay to prevent bus contention. In half‑duplex networks, ensure DE is asserted only after the last bit plus transmitter disable time; add inter‑byte dead time accordingly. Create a timing table of propagation delay, tEN, tDIS, and recommended inter‑frame spacing and place test points on DI, RO and the A/B pair for oscilloscope verification.

4 — Common Use Cases & Application Circuits (Case)

Typical application: point-to-point and multi-drop RS-485 networks

Standard practice for multi‑drop RS‑485: terminate at the ends with 120Ω across A and B, implement biasing resistors to provide a fail‑safe idle differential, and minimize stubs by using a single trunk with short taps. A compact example circuit includes the transceiver, 0.1µF decoupling, 120Ω end terminations, and two pull resistors (pull‑up on A, pull‑down on B) sized to guarantee idle voltage within the receiver’s thresholds under worst‑case loading.

Long-haul, repeaters and special topologies

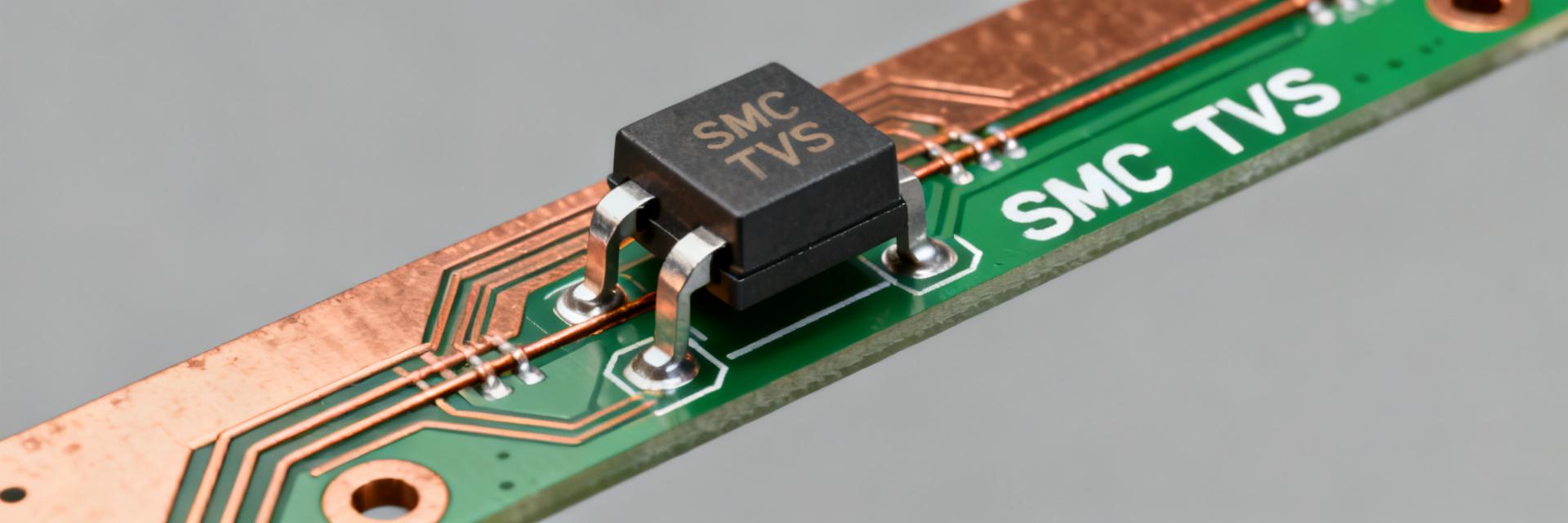

For long cable runs, consider segmentation with repeaters or isolated transceivers and keep impedance continuity. Limit node counts per segment, add ESD/transient protection at entry points, and consider temperature and surge stresses in component derating. A practical long‑distance schematic layers termination, biasing and a simple surge clamp plus common‑mode choke if required for high‑noise environments.

5 — Design, Troubleshooting & Integration Best Practices (Action)

PCB layout & EMI mitigation

- Route A/B as a controlled differential pair.

- Place termination only at extreme ends.

- Use a single ground plane.

- Add common‑mode chokes for noisy environments.

- From the slew‑rate specs, add small series resistors.

Debug checklist

- Verify power rails and decoupling.

- Perform local loopback on DI/RO pins.

- Capture A/B waveforms on oscilloscope.

- Check for contention (both drivers active).

- Verify termination and stub length.

Summary

The MAX483CSA provides a low‑power, slew‑rate‑controlled RS‑485/RS‑422 solution suitable for reliable multi‑drop and long‑haul links when properly terminated and laid out. Key actionable checks from the datasheet are supply and thermal margins, DE/RE timing, termination and biasing strategy, and oscilloscope‑based validation of driver edges and bus integrity. Use the provided layout and commissioning checklist as a starting point to reduce EMI, avoid contention, and ensure field reliability for serial networks using this transceiver.

Key Summary

- MAX483CSA design focus: verify recommended VCC and thermal derating from the datasheet before committing to boards; check ICC and power dissipation numbers against worst‑case ambient.

- Pinout & layout: place decoupling close to VCC/GND, route A/B as matched differential pair, and use end‑of‑line 120Ω termination with proper biasing for fail‑safe idle.

- Timing & EMI: read propagation and enable/disable times to size inter‑byte delays, and apply series resistors or RC filtering based on the listed slew‑rate behavior to limit EMI and ringing.

FAQ

Q What are the key electrical limits to check in the MAX483CSA datasheet?

Check recommended operating voltage, absolute‑maximum ratings, ICC (idle and active), thermal resistance, and driver output characteristics. Use these to compute worst‑case power dissipation and ensure junction temperature stays below rated limits with margin; also inspect common‑mode range and receiver thresholds for system compatibility.

Q How do I interpret the MAX483CSA pinout for PCB layout?

Map DE, RE, DI, RO, A, B, VCC and GND to the footprint precisely. Place the 0.1µF decoupling capacitor adjacent to VCC and GND pins, stitch ground vias near the device pad, and keep differential pair symmetry. Label test points for DI, RO and the A/B pair to simplify oscilloscope debugging.

Q How should I test and debug a network using this transceiver?

Start with power rail verification and loopback tests, then capture differential waveforms for A/B and DE timing on a scope. Validate termination and bias resistors, check for bus contention by monitoring RO and driver outputs during multi‑node communications, and address reflections or EMI with termination adjustments or series damping.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP