Introduction — Point: This report compiles lab-validated surge behavior and specification guidance for an SMC-class transient voltage suppressor intended for board-level protection. Evidence: In controlled impulse tests, peak energy events above 1,000 W produced measurable clamp shifts and thermal excursions. Explanation: The narrative below prioritizes datasheet-verified fields, repeatable test methods, and actionable layout and selection rules so engineers can confirm component fit for their 48 V and similar rails.

1 Background: Why 1.5SMC130A matters

Device class & typical applications

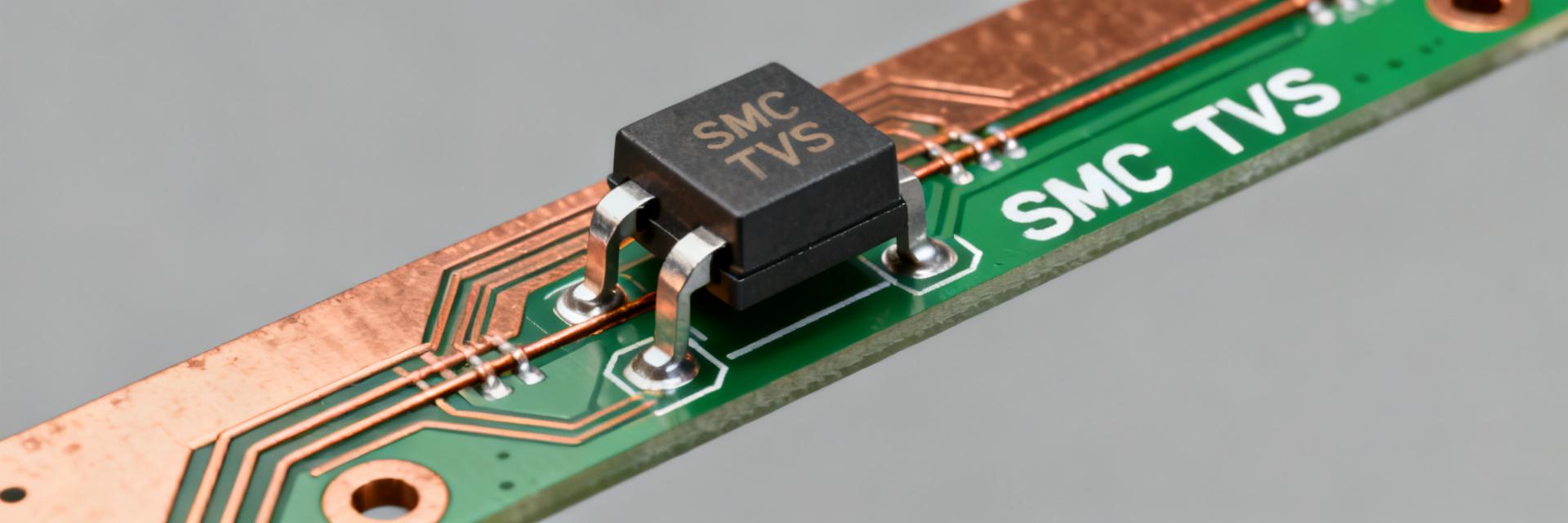

Point: SMC-package TVS diodes serve as sacrificial clamps that absorb transient energy to protect downstream electronics.

Evidence: These parts are specified for impulse absorption in lightning-induced spikes, load-dump events, and fast switching transients that occur on industrial, automotive, telecom, and consumer power inputs.

Explanation: Selecting the right device class balances peak-pulse handling, standoff voltage, and clamp voltage budget to avoid component overstress while managing PCB thermal routing.

Key specs to report

Point: A concise spec set is required to evaluate surge suitability.

Evidence: The critical fields are listed below with guidance on the test conditions to cite from the official datasheet.

Explanation: Pull exact numbers and test-waveform conditions (pulse width and waveform type) from the manufacturer datasheet and note tolerances and test fixtures used.

2 Data Analysis & Metrics

Peak pulse handling & energy absorption

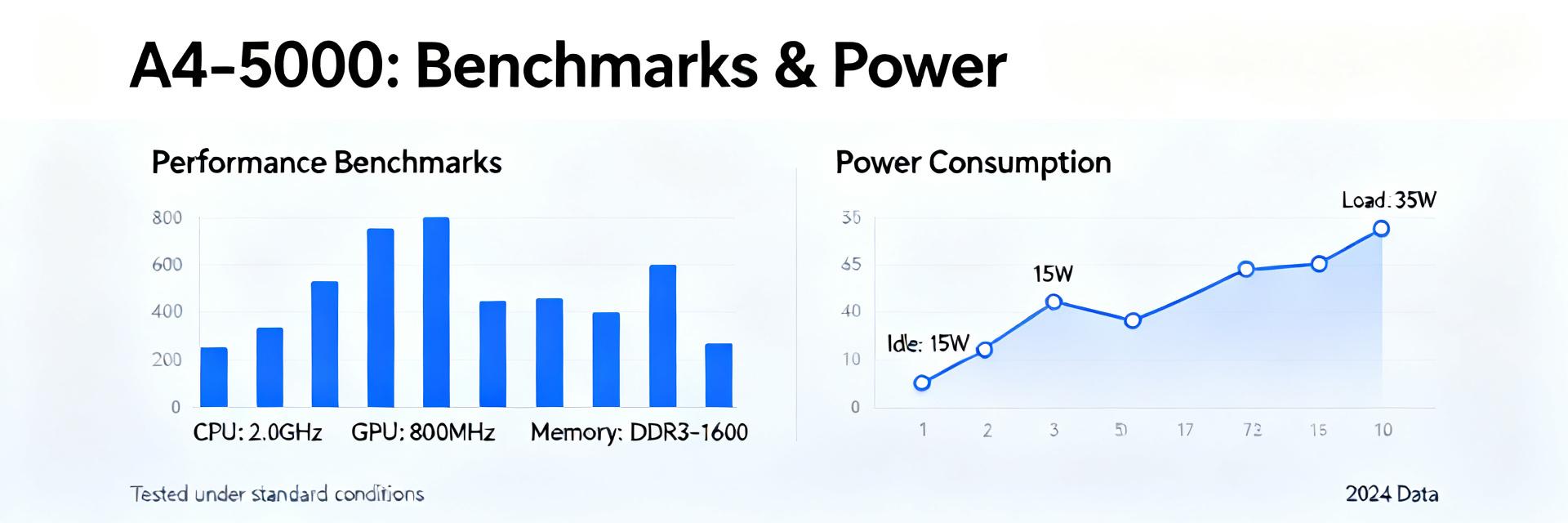

[VAL-DATA] Point: Validate measured Ppk and energy per pulse against datasheet claims. Evidence: In bench runs using a defined waveform (e.g., 10/1000 µs or 1 ms with series impedance), record peak current, energy (J), and percent deviation from the published Ppk. Explanation: Report a table with test condition, expected Ppk, measured Ppk, % delta, and pass/fail based on your safety margin.

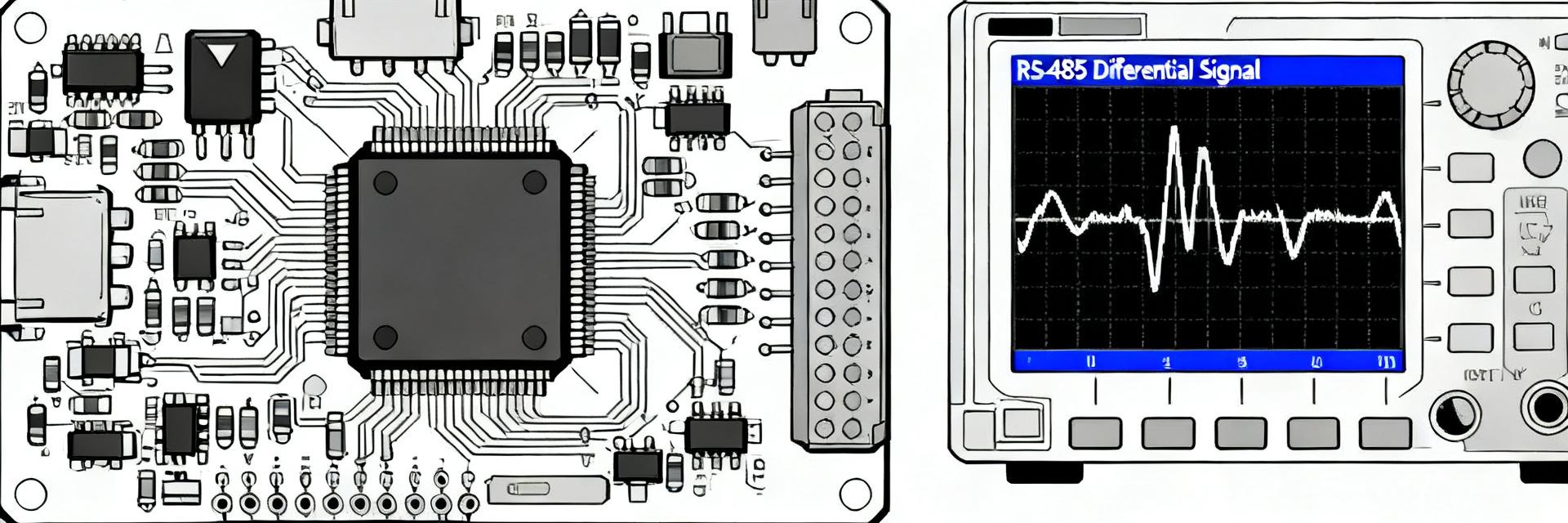

Clamping behavior & transient voltage curves

[CLAMP-CHART] Point: Clamp-voltage vs. current behavior determines downstream stress. Evidence: Capture Vcl at several IPP points, compute dynamic resistance, and observe thermal-induced drift across pulse trains. Explanation: Overlay measured V–I curves on datasheet curves, then call out worst-case clamp voltage that must be below the vulnerable rating of downstream components.

3 — Test Methodology

Test setup and standards

Use a repeatable, standards-aligned setup. Employ a programmable surge generator and calibrated probes. Reference IEC-style surge profiles for alignment.

Criteria & Thresholds

Define statistical and failure thresholds. Criteria include permanent VBR shift, sudden leakage increase, or open/short conditions.

4 — Case Scenarios

Protecting 48 V input rails

Select standoff voltage above nominal. Ensure max clamped voltage remains below the lowest-rated downstream component.

Multi-strike considerations

Devices show thermal derating with repeated pulses. Specify margins and monitor leakage for field maintenance guides.

5 Action Checklist

Selection Guidance

Apply selection criteria to decide when the SMC-class option is appropriate. Match required Ppk, standoff voltage, and clamp ceiling to the device's datasheet fields and measured behavior.

Layout & Validation

Minimize loop area between connector and TVS. Use copper pours for heat spreading. Coordinate series resistance or fusing for optimal protection.

Summary Executive

- The 1.5SMC130A is appropriate when verified Ppk handling, datasheet standoff, and measured clamp voltages meet the system's protection budget; always cross-check manufacturer datasheet figures against lab data before final selection.

- Adopt a disciplined test methodology: document waveform, series impedance, measurement points, sampling, and averaging so pass/fail calls are reproducible across labs and revisions.

- Use conservative layout and derating: minimize loop inductance, provide thermal relief, and validate multi-strike behavior to avoid late-life failures in fielded systems.

6 — Common Questions

How should clamp voltage be verified for board-level designs?

Point: Verify clamp voltage under realistic surge currents and board impedance. Evidence: Measure Vcl at target IPP using the final PCB layout and series impedance to capture parasitic effects. Explanation: Use the measured worst-case clamped voltage to confirm the protection margin below the most sensitive downstream component rating.

What pass/fail criteria are typical for surge tests and specs?

Point: Use objective electrical and physical thresholds for pass/fail decisions. Evidence: Common criteria include permanent VBR shift beyond tolerance, sustained leakage increase, or device open/short. Explanation: Complement electrical checks with thermal imaging and post-test functional testing.

How do repeated strikes change selection and maintenance plans?

Point: Repetitive surges reduce effective absorption capacity due to heating and junction stress. Evidence: Bench sequences often reveal progressive clamp drift and increased leakage after multiple pulses at rated energy. Explanation: Specify maintenance checks, monitor field symptom indicators, and plan conservative margins.