-

- Contact Us

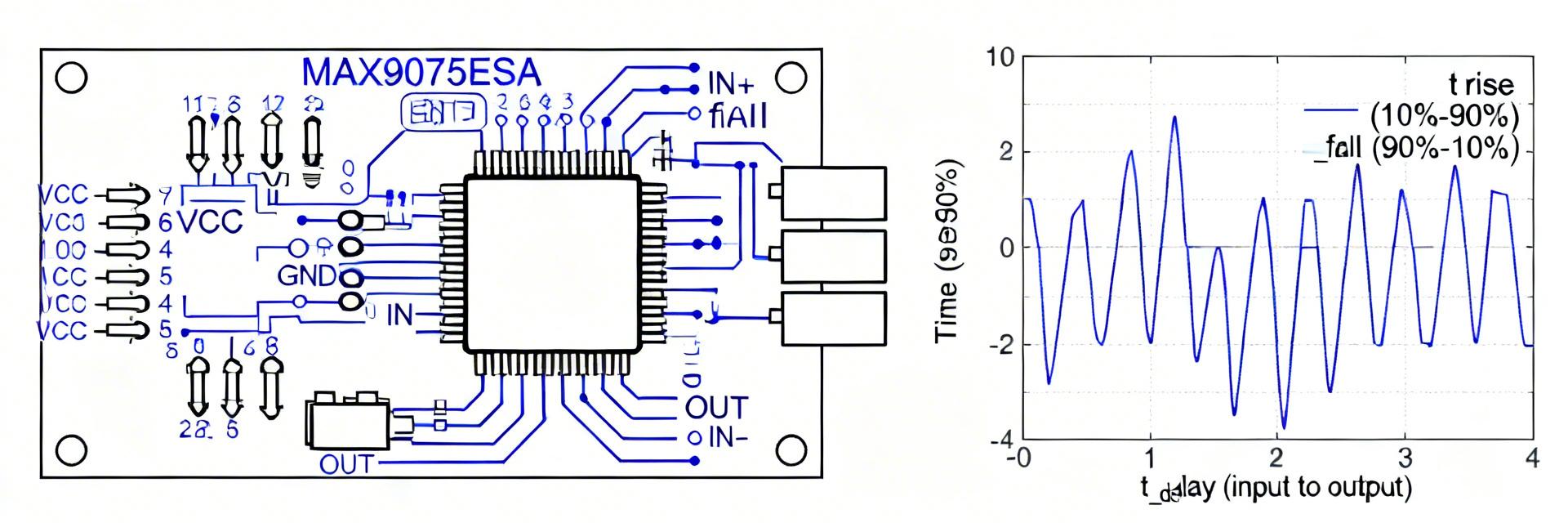

MAX9075ESA Comparator: Complete Datasheet & Pinout Guide

MAX9075ESA Comparator: Complete Datasheet & Pinout Guide

The MAX9075ESA is an ultra-low-power comparator offering typical propagation delay around 580 ns and supply current under 3 µA per comparator, optimized for single-supply operation between 3 V and 5 V. This guide delivers a concise pinout, the most important electrical characteristics pulled from the datasheet, practical example circuits, and a pre-production design checklist so you can integrate the device quickly and reliably.

Readers will get clear pin role definitions, prioritized parameter explanations, PCB layout rules (including decoupling values and placement), three reference circuits with expected behavior, and targeted troubleshooting steps for common comparator issues.

1 — Overview & Background (type: background introduction)

What the MAX9075ESA is and where it fits

Point: This family targets battery-powered and space-constrained designs requiring very low quiescent current. Evidence: Designers commonly choose tiny comparators for threshold detection, battery monitors, and wake-up circuits. Explanation: The device’s low supply current and single-supply operation make it ideal for sensor nodes and handheld electronics where sleep current and package size dominate trade-offs.

Key performance at a glance (spec summary)

- Supply voltage range: 3.0 V to 5.0 V (single-supply focus) — check datasheet for absolute limits and recommended operating range.

- Propagation delay: typical ~580 ns (specify test conditions when quoting timing numbers).

- Input common-mode range: includes ground to (VCC – ~1.2 V) typical — impacts rail-to-rail detection capability.

- Output type: push-pull or open-drain variants; note logic-level compatibility with interfaced MCU.

- Supply current: ≤3 µA per comparator typical; important for battery life calculations (use typical vs. max values from datasheet).

- Package options: ultra-small SOT/SOT-23/SC70 style packages — verify package drawing for pin numbering.

2 — Electrical Characteristics & Data Analysis (type: data analysis)

Detailed electrical parameters to prioritize

Point: Prioritize absolute maximum ratings, DC offsets, input bias, common-mode limits, AC timing, and supply current. Evidence: The datasheet organizes these in separate tables (DC characteristics, AC characteristics, power). Explanation: Offset voltage and input bias determine detection accuracy; propagation delay and rise/fall times set timing margins; quiescent current sets battery lifetime — trade speed vs. power when selecting hysteresis or pull-ups.

Typical waveforms and measurement conditions

Point: Timing numbers depend strongly on VCC, input step amplitude, and load conditions. Evidence: Datasheet graphs typically show delay vs. VCC and supply current vs. temperature under specific loads. Explanation: When reproducing or annotating waveforms, state test VCC, input step (e.g., 100 mV to 1 V), load resistor or capacitive load. Annotate thresholds and measurement probe locations so readers can correlate lab results to datasheet curves.

3 — Pinout, Package and PCB Footprint Guide (type: method guide / pinout focus)

Pinout breakdown by package (pin functions & recommended labels)

Point: Typical small-package pin roles include IN+, IN−, VCC, GND, OUTPUT, and possible NC or substrate pins. Evidence: For tiny SOT/SC70 parts the exposed pad or NC may be present; pin numbering varies by package. Explanation: Label silk for IN+, IN−, VCC and GND clearly; treat NC pins as no-connect unless datasheet indicates otherwise. For the MAX9075ESA expect one comparator output per channel and map pins per the package drawing in the official documentation.

PCB footprint, pad land pattern, and layout best practices

Point: Proper decoupling and layout minimize noise and offset. Evidence: Place a 0.1 µF ceramic decoupling capacitor within 2 mm of the VCC pin to GND. Explanation: Use a solid ground pour beneath the device, stitch ground with vias, and keep input traces short and away from high-speed signals. If an exposed thermal pad exists, follow pad solder and stencil recommendations; otherwise avoid large copper under the part that could shift solder fillet and introduce mechanical stress.

4 — Typical Application Circuits & Use Cases (type: case display)

Reference circuits and connection examples

Point: Three compact example circuits cover common needs. Evidence: Example A — single-ended threshold detector: IN+ via divider to sensing node, IN− to reference; add small hysteresis resistor for stability. Example B — push-pull output to MCU: direct connection if logic levels match; include series resistor to limit ringing. Example C — open-drain with pull-up for level translation: select pull-up to target logic voltage and watch current during switching. Explanation: For each, list component values and expected response times and note that hysteresis values trade sensitivity for stability.

Troubleshooting common implementation issues

Point: Oscillation at threshold, incorrect logic levels, and bounce are common. Evidence: Quick fixes: add hysteresis (10 kΩ to 1 MΩ range depending on threshold), add input RC filtering (e.g., 10 kΩ + 100 pF), verify pull-up value for open-drain outputs (10 kΩ–100 kΩ). Explanation: Use a bench checklist: probe inputs and output, sweep input slowly to identify hysteresis, swap comparator channel or board area to isolate layout issues, and verify supply decoupling under dynamic conditions.

5 — How to Read the Datasheet & Design Checklist (type: method / action)

Step-by-step datasheet reading map for engineers

Point: Read sections in order: absolute maximum ratings, recommended operating conditions, DC and AC characteristics, typical applications, package drawings, and ordering codes. Evidence: Extract must-have numbers for BOM: supply range, max input voltages, offset, propagation delay, supply current, and output drive capability. Explanation: Create a short table in your spec sheet listing these values with test conditions so procurement and test teams have precise targets.

Pre-production verification and validation checklist

Point: Run pre-layout and post-layout checks and bench validation. Evidence: Layout checks: footprint verification, decoupling placement, short input trace routing, and ground stitching. Bench tests: threshold sweep, propagation-delay measurement with defined load, temperature sweep across expected ambient range, and EMC quick checks. Explanation: Record test vectors, expected voltages at probe points, and acceptance criteria; iterate PCB changes based on measured offsets and timing under real load.

Summary (conclusion)

- Concise pinout reference and recommended footprint practices help avoid layout-induced offsets and oscillation; place a 0.1 µF decoupler within 2 mm of VCC and route inputs short and direct.

- Key electrical parameters to watch in the datasheet are offset, input common-mode range, propagation delay, and quiescent current — these determine accuracy, compatibility, speed, and battery life.

- Three practical circuits (threshold detector, MCU interface, open-drain translator) cover typical use cases; add hysteresis or RC filtering to resolve oscillation and contact bounce.

- Use the provided checklist to extract numbers from the datasheet and validate on the bench before production to reduce integration risk with the MAX9075ESA and its pinout requirements.

FAQ

What is the typical propagation delay for this comparator?

Typical propagation delay is on the order of several hundred nanoseconds under nominal VCC and with standard load; reproduce timing under your actual load and supply conditions as delay varies with VCC and output loading. Measure using a fast input step and a high-impedance oscilloscope probe.

How should I wire the comparator for open-drain output?

Use an external pull-up to the desired logic rail; choose pull-up resistance to balance speed and power (10 kΩ–100 kΩ typical). Ensure the pull-up voltage does not exceed the comparator’s maximum output rating and verify logic-level compatibility with the receiving device.

What decoupling is recommended for reliable operation?

Place a 0.1 µF ceramic capacitor from VCC to GND as close as possible (ideally within 2 mm) to the supply pin. For noisy supplies add a 1 µF bulk capacitor nearby. Good ground stitching and short traces minimize transient-induced errors.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP