-

- Contact Us

ABS10A-13 Datasheet Deep Dive: Specs & Insights for Engineers

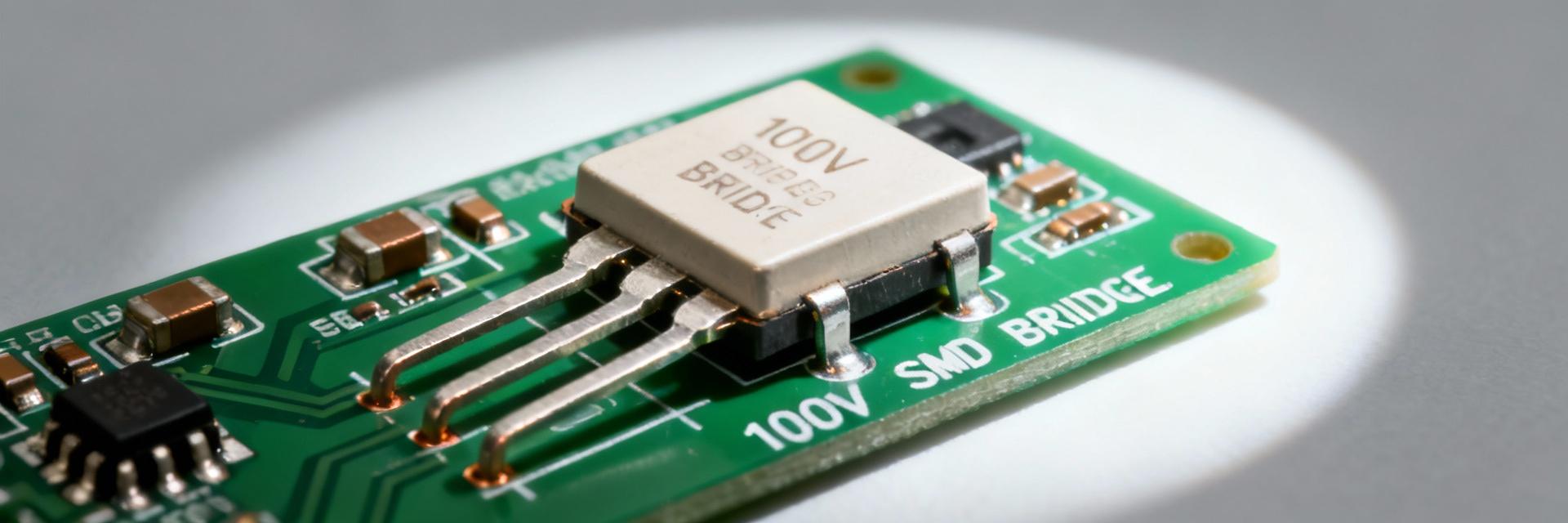

The ABS10A-13 is a 1.0 A surface-mount glass-passivated bridge rectifier rated for high blocking voltage—peak repetitive reverse voltage up to 1000 V—and characterized by a maximum forward voltage around 1.1 V at 1 A and reverse leakage down to single-digit microamperes at full PRV. These headline numbers are the practical starting point every design engineer needs when reading the ABS10A-13 datasheet and translating lab figures into board-level decisions. This article walks engineers through the critical datasheet entries, shows how to apply the specs in real designs (loss, thermal, surge), and gives practical test, sourcing, and substitution guidance you can act on in pre-production.

1 — ABS10A-13 at a glance (Background)

Key datasheet numbers and what they mean

Point: The must-capture metrics from the ABS10A-13 datasheet are Io (1.0 A), maximum forward voltage Vf (≈1.1 V @ 1 A), peak repetitive reverse voltage (PRV) up to 1000 V, reverse leakage (µA scale at high VR), non-repetitive surge current IFSM, and operating junction temperature limits. Evidence: The manufacturer’s datasheet lists these ratings as the device’s electrical and thermal boundaries. Explanation: For design use, Io sets continuous RMS conduction capability, Vf governs conduction loss (Pcond ≈ Vf × I), PRV defines blocking safety for mains-derived isolation, and leakage and IFSM determine suitability for high-voltage low-current sensing versus surge-prone mains front ends. Capture these numbers in your component spec sheet before layout or procurement.

Package, footprint and mechanical details

Point: ABS10A-13 is supplied in a compact SMD bridge package common to low-power rectifiers (check SOPA-4 / SMD outline in the datasheet). Evidence: Package drawings in the mechanical section identify pad pitch, overall dimensions, and polarity markings. Explanation: On the PCB, verify pad land dimensions against the manufacturer mechanical drawing, mark polarity clearly (corner pad or molded triangle), and adjust pad-to-pad spacing for high-voltage creepage if using the 1000 V rating. For reliable reflow, follow the solder paste stencil recommendations and note any thermal pad or courtyard callouts on your fab drawing.

Typical applications and selection rationale

Point: Typical uses include AC→DC bridge for small SMPS, high-voltage LED drivers, chargers, and mains sensing circuits where voltage headroom is primary and currents are modest. Evidence: The device’s 1 A continuous rating with high PRV makes it a natural fit for low-power, high-voltage lines. Explanation: Choose ABS10A-13 when you need high blocking voltage with compact SMD packaging; avoid it if continuous currents approach the multi-amp range or if Vf-related power loss cannot be tolerated. For example, a low-current LED driver that needs 700–900 V blocking with

| Parameter | Typical / Max |

|---|---|

| Continuous forward current (Io) | 1.0 A |

| Max forward voltage (Vf) | ≈1.1 V @ 1 A |

| Peak Repetitive Reverse Voltage (PRV) | Up to 1000 V |

| Reverse leakage | ~5 µA @ 1000 V (typical order) |

| Package | SOPA-4 / SMD bridge |

2 — Electrical characteristics deep-dive (Data analysis)

Forward behavior: Vf, dynamic resistance, and power dissipation

Point: Forward conduction loss is the product of Vf and forward current; dynamic resistance and temperature dependence modify Vf across operating ranges. Evidence: Datasheet Vf vs If curves and typical dynamic resistance entries quantify how Vf climbs with current and temperature. Explanation: Use Pcond = Vf × I to estimate steady-state loss. Worked example: at 0.5 A, if Vf is 0.9–1.0 V (interpolated from the Vf curve), Pcond ≈ 0.5 A × 1.0 V = 0.5 W. Account for temperature—Vf typically increases with junction temperature for silicon rectifiers, so thermal rise can increase loss slightly and feed back into junction temperature. Include dynamic resistance in transient models for accurate drop predictions in pulse conditions.

Reverse specs: PRV, VRRM, leakage and avalanche considerations

Point: Peak Repetitive Reverse Voltage (PRV) defines the maximum continuous reverse stress the part can see; datasheet curves clarify non-repetitive limits and avalanche behavior. Evidence: The datasheet differentiates PRV ratings and provides leakage vs. VR and temperature plots. Explanation: For high-voltage, low-current circuits, leakage matters more than conduction loss; a few microamperes of leakage at 1000 V can bias sensitive measurement nodes. Use a safety margin—typically 20–30% above expected peak reverse stress—when selecting VR to accommodate voltage spikes and manufacturing tolerance. Avoid operating at the absolute PRV limit without adequate transient suppression.

Transient & surge performance (IFSM, non-repetitive surge)

Point: IFSM (peak non-repetitive forward surge current) describes the device’s ability to survive short high-current pulses, often specified for a half-sinewave of 8.3 ms for mains surge testing. Evidence: Datasheet surge curves and IFSM ratings indicate allowable short-duration currents and thermal limits. Explanation: Read the IFSM curve to determine whether expected inrush or fault currents (e.g., capacitor charging or transformer magnetizing inrush) exceed the device’s capability. If near or above, add soft-start, inrush limiting, or a snubber; for repeated surges, choose a part with higher IFSM or derate Io to reduce stress. Always calculate energy (I^2·t) for the expected waveform and compare to datasheet non-repetitive-energy curves.

3 — Thermal, derating & reliability (Data analysis / Method)

Thermal resistance, junction temp, and derating curves

Point: Junction temperature Tj = Ta + P × RθJA (or use RθJC plus heatsink path) is the primary thermal relation; derating curves show allowable Io vs ambient. Evidence: Datasheet provides RθJA / RθJC and derating guidance; combine with measured or estimated dissipation to compute Tj. Explanation: Example method—if Pcond = 0.5 W and RθJA = 60 °C/W (confirm exact datasheet value), ΔTj ≈ 30 °C; at Ta = 60 °C, Tj ≈ 90 °C which is within typical silicon limits. Use datasheet derating curves to reduce continuous Io at elevated ambient: many SMD bridge rectifiers require derating above a baseline temperature (check the curve) to preserve long-term reliability.

PCB mounting, thermal vias and practical cooling tips

Point: Board-level thermal management—copper pours, thermal vias, solder volume—significantly affects RθJA and thus junction temperature. Evidence: Manufacturer layout recommendations and general SMD thermal practice show pad sizes and via patterns to reduce thermal resistance. Explanation: To lower junction temperature, maximize copper area connected to the device’s pads, add thermal vias under large pads to inner or back-side copper planes, and avoid isolated small pads. For reflow, respect profile recommendations to ensure full wetting; inconsistent soldering raises contact resistance and worsens thermal paths. Include thermal validation steps (IR thermography, in-situ Tj measurement) in your sign-off plan.

Reliability, operating limits and failure modes

Point: Typical operating junction ranges are broad (for many silicon devices from about −55 °C to +150 °C storage and similar operating limits); common failures include thermal overstress and surge-induced junction degradation. Evidence: Datasheet specifies operating and storage temperature ranges and notes on non-repetitive stress. Explanation: Mitigate failure modes by ensuring Tj stays well below max during worst-case ambient and power dissipation, by limiting repetitive surge exposure, and by applying appropriate burn-in or thermal-cycle tests during qualification. For long-life designs, target average operating temperatures well below maximum to improve MTBF.

4 — Test procedures & bench validation (Method / Action)

How to measure Vf, reverse leakage, and PIV safely

Point: Use controlled current sources and high-voltage sources with limited energy for PIV testing; measure Vf with a precision supply and series sense resistor, and measure leakage with a picoammeter at rated VR. Evidence: Standard bench practice and datasheet test conditions call out currents, pulse durations, and measurement temperatures. Explanation: For Vf measure at 1 A, use a source capable of delivering the current and measure the drop across the diode with a four-wire sense if possible. For reverse leakage and PIV, ramp voltage slowly while monitoring current; use HV supplies with current limiting to avoid destructive avalanching. Note pass/fail thresholds from the datasheet and log temperature during measurement, as leakage scales with Tj.

Surge, ESD and thermal cycling test protocols

Point: Define test sequences that replicate expected field stress—single short surge (IFSM-style), ESD contact/discharge checks, and thermal cycling to rated extremes. Evidence: Datasheet surge specs and industry test standards guide waveform selection and cycle counts. Explanation: Execute controlled surge tests (e.g., half-sine 8.3 ms) while monitoring device Vf and leakage before/after; use ESD testers for IEC-style levels relevant to your product. For thermal cycling, use the junction/storage ranges from the datasheet and inspect for drift versus catastrophic failure. Record results in a test report with pre/post electrical characteristics for traceability.

Troubleshooting discrepancies between datasheet and measured behavior

Point: Discrepancies often stem from measurement setup, soldering damage, lot variation, or temperature misestimation. Evidence: Common root causes are documented in field reports and supplier application notes. Explanation: Isolate issues by cross-checking fixtures (four-wire, recommended sweep rates), swapping to a fresh sample from a different reel, and inspecting solder joints and package markings. If behavior persists, gather full test logs, photos, lot/date codes, and waveform captures before contacting supplier support—this speeds root-cause analysis and warranty/quality handling.

5 — Sourcing, alternatives and design checklist (Case study / Action)

Comparing ABS10A-13 to similar bridge rectifiers

Point: When substituting, match PRV, Io, Vf, package, and thermal resistance; differences in RθJA or leadframe can break thermal equivalence. Evidence: Side-by-side spec comparisons show identical VR and Io do not guarantee equal thermal performance. Explanation: Create a short spec-comparison table for candidate parts and prioritize matching PRV and Io first, then Vf and package. If RθJA differs, run thermal simulations or margin the Io downward. For drop-in replacement, ensure mechanical pad compatibility and reflow profile compatibility.

| MPN | PRV (V) | Io (A) | Vf @1A (V) | Package |

|---|---|---|---|---|

| ABS10A-13 | 1000 | 1.0 | 1.1 | SMD bridge |

| Competitor X | 600 | 1.0 | 1.0 | SMD bridge |

Procurement, packaging, and counterfeit checks

Point: Order from authorized distributors, track reel/lot codes, and inspect incoming parts for visual anomalies. Evidence: Distributor traceability and manufacturer packaging notes reduce counterfeit risk. Explanation: Typical packaging is tape-and-reel for SMD bridges; verify part markings, packaging seals, and date codes. Red flags include inconsistent marking, unusual finish, or price significantly below market. Implement basic incoming tests (Vf spot check, leakage at VR) for suspect lots before assembly to avoid rework.

Pre-production design checklist & recommended BOM notes

Point: Consolidate footprint checks, thermal simulation, bench verification, derating confirmation, and supplier qualification into a pre-PN checklist. Evidence: Design for manufacturability and quality control best practices recommend these steps. Explanation: Suggested BOM line: exact MPN, manufacturer name, package, and approved alternates with distinct part numbers. Checklist items: verify mechanical drawing vs footprint, run thermal sims at worst-case power, bench test samples for Vf/leakage/IFSM, confirm derating at expected ambient, and qualify supplier traceability.

Summary

- The ABS10A-13 provides 1.0 A continuous current and high blocking capability (1000 V PRV), making it suitable for low-current, high-voltage AC→DC bridge roles where compact SMD form factor matters; confirm Vf and leakage tradeoffs before commit.

- Use Vf × I for conduction loss estimates, combine with RθJA to predict junction temperature, and apply a 20–30% VR margin for transient headroom; always check the manufacturer datasheet for precise Rθ and surge curves.

- Validate with bench tests (Vf at 1 A, leakage at rated VR, IFSM surge tests), implement PCB thermal best practices (copper pours, vias), and enforce procurement checks for traceability and counterfeit avoidance.

FAQ

What are the key specs in the ABS10A-13 datasheet I should record?

Record Io (1.0 A), Vf at relevant test current (≈1.1 V @ 1 A), PRV/VR rating (1000 V), reverse leakage at VR and temperature, IFSM surge rating and the specified waveform, package outline, and RθJA/RθJC. These fields let you simulate loss, thermal rise, surge tolerance, and PCB layout implications.

How do I calculate junction temperature for ABS10A-13 in my board layout?

Compute Tj = Ta + P × RθJA where P ≈ Vf × I + switching or ripple losses. Use the datasheet RθJA for the recommended mounting; if you added copper pours or vias, measure RθJA in a thermal test coupon. Validate with IR or junction-sensing techniques during prototype to ensure design margins.

Can I drop in a different bridge for ABS10A-13 without revalidation?

Only if the substitute matches PRV, Io, Vf, package footprint, and thermal resistance. Even then, differences in RθJA or mechanical leadframe can change thermal performance—revalidation (thermal and surge tests) is strongly recommended before production to avoid field failures.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP