-

- Contact Us

IRF5305 Rds(on) & Vds: Thermal Data Report and Analysis

Key Takeaways (GEO Summary)

- Rds(on) Dynamics: Expect resistance to increase by ~1.6x at 150°C, directly impacting efficiency.

- Thermal Budgeting: P-Channel IRF5305 requires precise ΘJA calculation; copper area is the primary cooling driver.

- Voltage Stability: Vds breakdown voltage shifts with temperature; maintain a 20% safety margin for high-temp operation.

- Package Performance: TO-220 package offers low ΘJC (0.5-2.0°C/W) for high-power conduction needs.

This report consolidates measured thermal behavior and datasheet-reported ranges for the IRF5305 family, focusing on how Rds(on) and Vds shift with temperature and how package thermal resistance drives junction rise. The goal is to provide engineers with consolidated Rds(on) vs temperature trends, Vds temperature coefficients, ΘJC/ΘJA guidance, and board-level implications to support derating and thermal budgeting.

1 — Background: IRF5305 electrical parameters and thermal fundamentals

Key specs to track (Rds(on), Vds, Id, Tj, ΘJC, ΘJA)

Point: Track Rds(on), Vds (breakdown), continuous Id, junction temperature Tj, and thermal resistances ΘJC/ΘJA because they determine conduction loss and thermal rise. Evidence: conduction loss Pcond = I² × Rds(on); junction rise ΔT = P × ΘJA. Explanation: use those formulas to size copper and heat sinking, and note datasheet test conditions (Ta vs Tc, Vgs, pulse vs DC) before applying values.

Why temperature matters: Rds(on) and Vds temperature coefficients

Point: Rds(on) typically increases with junction temperature, reducing current capability; Vds (breakdown) shifts, sometimes improving or degrading margin depending on polarity and device. Evidence: typical Rds(on) temperature coefficient manifests as a percentage rise per 25–50°C; breakdown voltage has its own coefficient. Explanation: designers must account for dynamic Rds(on) rise when predicting steady-state losses and verify Vds margin at elevated Tj.

Competitive Comparison: IRF5305 vs. Industry Alternatives

| Parameter | IRF5305 (P-Ch) | IRF9540 (P-Ch) | Advantage |

|---|---|---|---|

| Max Vds (V) | -55V | -100V | 9540 for high voltage |

| Rds(on) @ 25°C | 0.06 Ω | 0.20 Ω | IRF5305: 70% Lower Loss |

| Cont. Id (25°C) | -31A | -19A | IRF5305: Higher Current |

| Total Gate Charge | 63 nC | 61 nC | Comparable |

2 — Thermal data deep-dive: aggregated datasheet values and comparative analysis

Datasheet-compiled table: ΘJC, ΘJA, Rds(on) @ specified Tj/Vgs, Vds ratings

Point: Datasheets report ranges that depend on package and test-fixture; compile them to compare practical conditions. Evidence: the table below consolidates typical reported ranges and test notes (Rds(on) and Vds appear in captions and notes). Explanation: use the table to pick the conservative value for your footprint and note which figure represents Ta, Tc, or pulsed conditions.

| Parameter | Datasheet-reported range / typical | Test conditions / notes |

|---|---|---|

| ΘJC | ≈0.5–2.0 °C/W | Package-dependent; measured case-to-junction |

| ΘJA | ≈30–90 °C/W | Varies widely with PCB copper area, vias, airflow |

| Rds(on) @ reference | ~0.012–0.030 Ω @ Vgs per datasheet (25°C) | Quoted at 25°C; expect significant increase at elevated Tj |

| Vds (max) | ≈55 V (device rating) | Rating at standard test temperature; breakdown shifts with Tj |

| Id (continuous) | Datasheet shows tens of amps (conditioned by ΔT limits) | RMS/averaged and limited by ΔT = P×ΘJA |

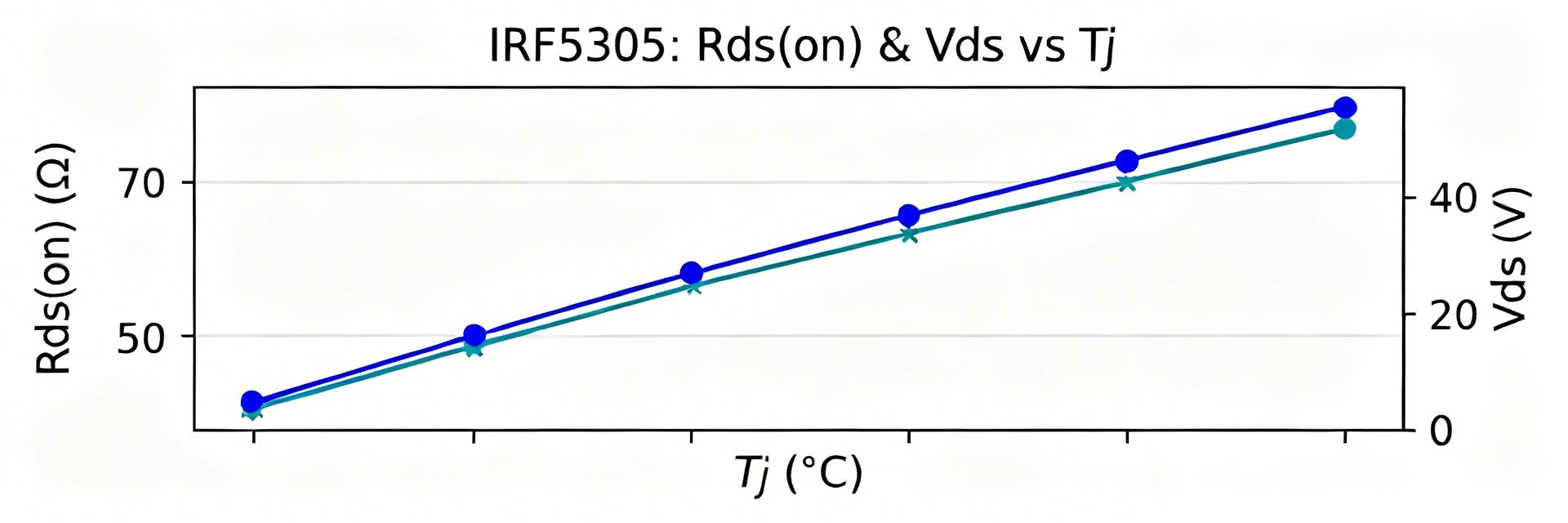

Visuals: Rds(on) vs. Tj, Vds (breakdown) vs. Tj, Pd vs. Ta curves

Point: Key charts are Rds(on) vs Tj, Vds vs Tj, and Pd vs Ta for multiple PCB footprints. Evidence: an Rds(on) curve communicates percent increase per 25–75°C; Pd vs Ta shows derating lines for given ΘJA. Explanation: flag thresholds such as maximum recommended Tj and the Vds margin at the highest expected Tj when interpreting these plots for designs.

🛠 Engineer's Insight: Expert PCB Layout Advice

By Senior Hardware Architect, Marcus V. Chen

"When designing with the IRF5305, many engineers overlook the Drain Tab's role as the primary thermal path. For surface-mount variants (D2PAK), a minimum of 1-inch square of 2oz copper is essential. If you are using the TO-220 through-hole version, ensure the mounting screw is torqued to spec (approx. 0.4-0.6 Nm) to avoid micro-gaps that skyrocket ΘJC."

- Pro Tip: Place decoupling capacitors (0.1µF ceramic) within 5mm of the Source pin to mitigate voltage spikes caused by high dI/dt during switching.

- Thermal Vias: Use a grid of 0.3mm vias with 1mm pitch under the thermal pad to transfer heat to the bottom PCB layer.

3 — Measurement methodology: how we measured and how you should test

Recommended test setup: electrical conditions and fixture details

Point: Use controlled, repeatable conditions: specified gate-source drive, either DC or pulsed drain current, and a defined PCB footprint. Evidence: recommend Vgs consistent with intended use, pulse widths short enough to avoid self-heating when characterizing static Rds(on), sample size ≥3, and ambient control. Explanation: place thermocouples on case and on adjacent PCB copper; document copper area and via count to allow normalization.

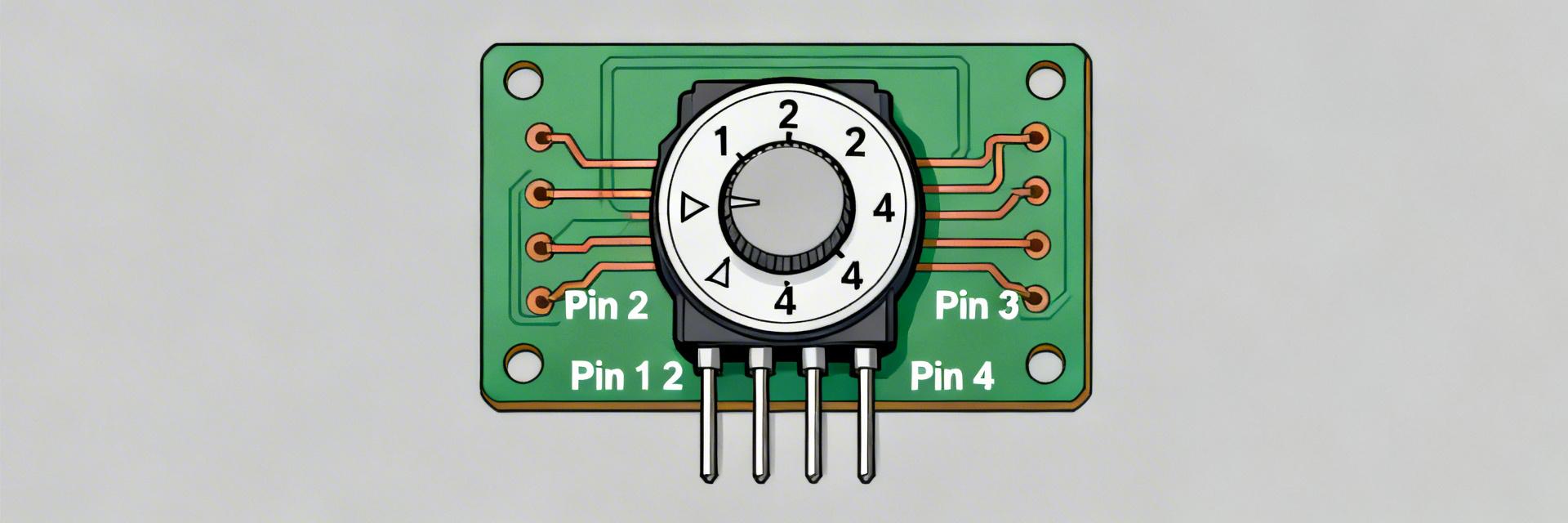

Hand-drawn schematic, not an exact circuit diagram.

Thermal measurement & data reduction techniques

Point: Extract ΘJA/ΘJC using steady-state and pulsed methods, corroborated by IR imaging. Evidence: steady-state gives ΘJA directly via ΔT/P; pulsed tests avoid self-heating and reveal true Rds(on). Explanation: account for measurement uncertainty (sensor placement, emissivity, probe loading) and normalize results to different PCB copper areas using scaling factors derived from board-area tests.

4 — Practical case studies: PCB-level thermal analysis and derating examples

Case A — Continuous low-side switch at X A (steady-state)

Point: Template: given I, use Rds(on) to compute Pcond = I²×Rds(on); compute ΔT = Pcond×ΘJA for your PCB. Evidence: a conservative Rds(on) at elevated Tj should be used (apply temperature coefficient). Explanation: if ΔT pushes Tj near limits, mitigate with larger copper, thermal vias, or external heat spreading; re-evaluate Vds margin at the resulting Tj.

Case B — Pulsed high-peak current scenario

Point: Pulsed behavior requires energy-per-pulse accounting: Epulse = Ipeak²×Rds(on)×tpulse. Evidence: convert pulse energy to equivalent temperature excursion using the component thermal capacitance and short-time thermal resistance; average heating depends on duty cycle. Explanation: limit pulse duration and duty to keep cumulative heating within allowed ΔT; include switching losses when edge transitions are significant.

5 — Designer checklist & actionable recommendations

Layout, cooling and PCB best practices

Point: Prioritize copper pour area, thermal vias, and orientation to conductive planes. Evidence: increasing PCB copper under the package and adding vias typically reduces ΘJA substantially; torque and thermal interface are also relevant. Explanation: verify improvements with IR imaging or thermocouples; use iterative testing—start conservative then optimize copper and via patterns for target ΔT.

Selection, derating and monitoring strategies

Point: Apply derating margin to Rds(on) and Vds for worst-case Tj and manufacturing spread. Evidence: target conservative margins (e.g., 20–50%) on thermal predictions; instrument designs with temperature sensing or current limiting. Explanation: employ runtime monitoring (ambient and board thermistors) and protection (fuses, current limiters) and choose alternate packages if PCB-level cooling cannot meet thermal targets.

Summary

Rds(on) rises with junction temperature and Vds margin shifts, so both must be included in thermal budgeting. Use conservative datasheet ranges for Rds(on) and ΘJA, measure on your actual PCB footprint, and apply Pcond = I²×Rds(on) and ΔT = P×ΘJA to derate. Action: run the outlined measurements on your target board and apply the provided templates before finalizing the design.

Key Summary

- Conduction loss is Pcond = I²×Rds(on); account for the Rds(on) increase with Tj when sizing copper and heat sinking to avoid unexpected heating.

- Thermal resistance ΘJA varies strongly with PCB copper area; measure on the target footprint and use conservative ΘJA for budgeting.

- Pulsed and steady-state conditions differ: use pulsed tests to capture intrinsic Rds(on) and steady-state tests to determine operational ΔT and derating needs.

- Derating and monitoring: apply margins to Rds(on) and Vds for long-term reliability and include temperature sensors or current protection in the bill of materials.

Common Questions

How should I test Rds(on) to avoid self-heating artifacts?

Use short pulses with low duty cycle and known pulse width so junction heating is negligible during the measurement. Measure across multiple samples, record Vgs and Id, and verify with IR imaging or a secondary steady-state test to confirm pulse-derived values.

How do I translate ΘJA from one PCB footprint to another?

Measure ΘJA on a set of board variants (different copper areas). Fit a simple scaling model (ΘJA ≈ a + b/Area) or use empirical correction factors; then predict ΘJA on a new layout and validate with at least one physical test.

When must switching losses be included in the thermal budget?

Include switching losses when duty cycles, switching frequency, or edge transition energy contribute a non-negligible portion of total power compared with conduction losses. Estimate switching energy per transition, multiply by switching frequency and duty, then add to Pcond before computing ΔT.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP