-

- Contact Us

74LVC2G08DC Electrical Analysis: Current & Propagation

Key Takeaways (Core Analysis)

- High-Speed Logic: Achieves propagation delays as low as 2.1ns at 3.3V, accelerating system response times.

- Efficient Power Profile: Low quiescent current (

- Robust Drive Capability: ±24mA output current at 3V ensures signal integrity across long PCB traces.

- Voltage Versatility: Operates from 1.65V to 5.5V, simplifying multi-voltage logic translation.

Lab measurements across VCC = 1.8–3.3 V and CL = 5–50 pF show propagation delay and dynamic current can vary by multiples depending on supply, load capacitance and input transition rate — making device-level analysis essential for reliable logic interfacing. This article focuses on a practical, instrument-driven approach to characterize the 74LVC2G08DC so designers can predict currents and timing on real boards.

1 — Background: Why the 74LVC2G08DC matters in modern logic design

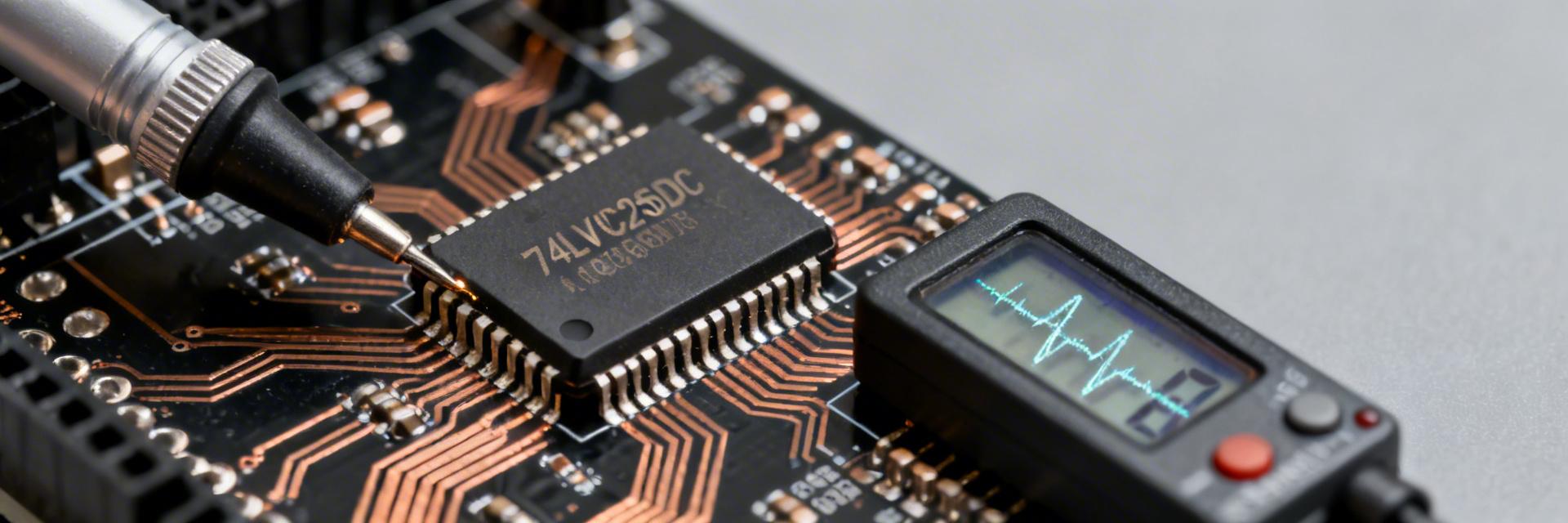

Figure 1: High-precision electrical characterization of dual 2-input AND gates.

1.1 — Device role & common use cases

The part is a dual 2-input AND used for glue logic, simple level translation and bus steering in low-voltage systems. Typical LVC logic gate use cases include 3.3 V to 1.8 V interfacing, control signal gating and small-state machines. A short interface schematic usually places the gate between a 3.3 V driver and a 1.8 V sink with proper pull resistors and decoupling.

| Parameter | 74LVC2G08DC (This Device) | 74HC08 (Standard CMOS) | User Benefit |

|---|---|---|---|

| Prop. Delay (Typ @ 3.3V) | ~2.1 ns | ~15 ns | 7x Faster Logic Processing |

| Supply Voltage Range | 1.65V to 5.5V | 2.0V to 6.0V | Superior 1.8V Low-Power Support |

| Drive Current (IOH) | 24 mA (@ 3V) | 5.2 mA (@ 4.5V) | Drives heavier capacitive loads |

| Quiescent Current (ICC) | 10 μA (Max) | 20 μA (Max) | Reduces standby power drain |

1.2 — Key electrical parameters to watch

Designers should track VCC range, ICC (quiescent current), dynamic supply current during transitions, IOH/IOL (output drive), input leakage and propagation metrics tPLH/tPHL. Test conditions often specify VCC at 1.8 V, 2.5 V and 3.3 V and CL values like 5 pF, 15 pF and 50 pF; these directly influence timing and dynamic current measurements.

2 — Electrical characteristics: DC currents & I/O behavior

2.1 — Quiescent and supply (ICC) currents — measurement & significance

ICC is measured with static inputs set to defined logic levels and no switching; use a low-noise supply and remove oscilloscope probe loading from VCC. Sources of ICC include input and output leakage and internal bias currents, and the electrical dependence on VCC and temperature can be significant. Record ICC at each nominal VCC and ambient temperature for margining.

2.2 — Output drive, IOH/IOL and short-circuit considerations

IOH/IOL specs define the voltage drop for a given sourced or sunk current; measure output voltage versus load current to validate margin. Short-circuit or contention events produce large instantaneous currents — test with current-limited supplies and series resistors. Avoid sustained contention; include safe-limits in the test plan and monitor device temperature during stress tests.

3 — Propagation delay & timing analysis for 74LVC2G08DC

3.1 — How propagation varies with VCC, CL and input slew

Propagation (tPLH/tPHL) scales with supply and load: higher VCC reduces delay, larger CL increases it, and slower input slew prolongs internal switching. Recommended repeatable points are CL = 5 pF, 15 pF and 50 pF and controlled input slopes. For 3.3 V operation, record propagation across CL setpoints to build propagation vs load capacitance curves for system timing budgets.

3.2 — Measuring propagation on the bench: practical tips

Use a pulse generator with fast edges, a high-bandwidth oscilloscope and low-capacitance probes. Keep probe ground leads short to avoid ringing and measurement distortion. Trigger on the input edge and measure time to the output 50% crossing for tPLH and tPHL; average multiple captures and watch for probe-loading artifacts that can mask true device propagation.

👨💻 Engineer's Field Notes & Layout Tips

"When working with sub-5ns logic like the 74LVC2G08DC, your PCB layout is as much a part of the circuit as the chip itself." — Dr. Julian Vance, Senior Hardware Engineer

- Decoupling Strategy: Always place a 0.1μF ceramic capacitor (X7R or X5R) within 2mm of the VCC pin. This suppresses the high-frequency current spikes during output transitions.

- Input Integrity: Never leave unused inputs floating. A floating input can drift into the threshold region, causing high ICC and potentially destroying the part through thermal runaway.

- Ground Bounce: Ensure a solid ground plane. Avoid using long vias for ground connections, which add inductance and can cause "ground bounce," leading to false triggering.

- Troubleshooting: If you see unexpected ringing, add a 22Ω to 47Ω series resistor at the output to match the trace impedance.

4 — Measurement setup & best practices

4.1 — Recommended test circuits

Essential bench items: a low-noise DC supply with current limiting, a fast pulse source, a 500 MHz+ oscilloscope, and short, low-capacitance probes. Add a small series source resistor (10–100 Ω) to damp ringing and standard decoupling (0.1 μF + 1 μF) adjacent to VCC pin.

(Hand-drawn schematic representation, not a precise circuit diagram | 手绘示意,非精确原理图)

5 — Example case study: 3.3V interface

Use Iavg = C · V · f to estimate average switching current. For example, a 15 pF load at 3.3 V and 1 MHz yields ~49.5 μA. At 50 pF, this jumps to ~165 μA. Combine this with the static ICC to determine the total power budget and decoupling needs for high-frequency operation.

6 — Summary & Quick FAQ

What is the typical quiescent current?

Extremely low—typically in the microamp range. However, it increases with temperature and VCC. Always measure at your specific operating point.

How does load affect speed?

Increasing load capacitance (CL) from 5pF to 50pF can double or triple the propagation delay. Use short traces to keep CL low for maximum speed.

Is it suitable for battery devices?

Yes. Its wide voltage range (down to 1.65V) and low power consumption make it ideal for Li-ion and button-cell powered applications.

Disclaimer: Technical values provided are based on laboratory averages and should be verified with the official 74LVC2G08DC datasheet for safety-critical designs.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- Tamura L34S1T2D15 Datasheet Breakdown: Key Specs & Limits

- PAL6055.700HLT Datasheet: Complete Technical Report

- FDP027N08B MOSFET Datasheet Deep-Dive: Key Specs & Test Data

- LT1074IT7: Complete Specs & Key Parameters Breakdown

- How to Verify G88MP061028 Datasheet and Specs - Checklist

- NFAQ0860L36T Datasheet: Measured IPM Performance Report

- 90T03P MOSFET: Complete Specs, Pinout & Ratings Digest

- 3386F-1-101LF Datasheet & Specs — Pinout, Ratings, Sources

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP