-

- 联系我们

- Cookies 政策

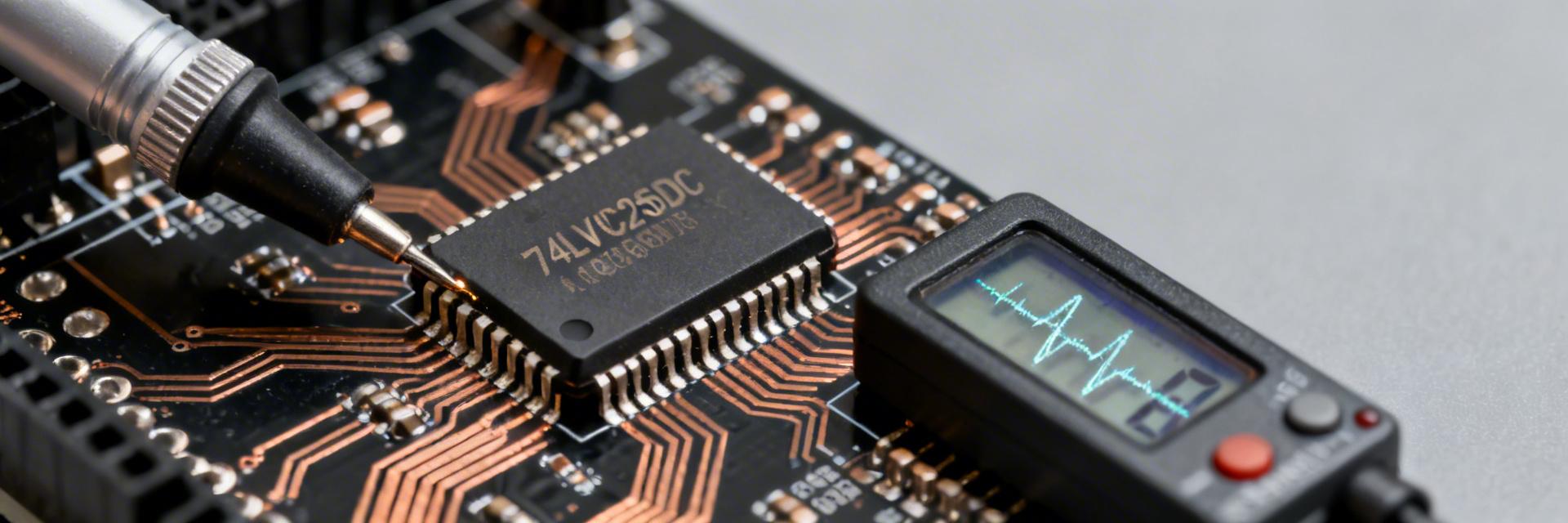

74LVC2G08DC 电气分析:电流与传播

关键摘要(核心分析)

- 高速逻辑:在 3.3V 下实现低至 2.1ns 的传输延迟,加速系统响应时间。

- 高效功耗特性:低静态电流(

- 强大的驱动能力:在 3V 下具有 ±24mA 的输出电流,确保长距离 PCB 走线的信号完整性。

- 电压通用性:工作电压范围为 1.65V 至 5.5V,简化了多电压逻辑转换。

在 VCC = 1.8–3.3 V 和 CL = 5–50 pF 范围内的实验室测量表明,传输延迟和动态电流可能会根据电源、负载电容和输入转换速率成倍变化,这使得器件级分析对于可靠的逻辑接口至关重要。本文重点介绍了一种实用的、仪器驱动的方法来表征 74LVC2G08DC,以便设计人员可以预测实际电路板上的电流和时序。

1 — 背景:为什么 74LVC2G08DC 在现代逻辑设计中至关重要

图 1:双 2 输入与门的高精度电气特性表征。

1.1 — 器件角色与常见用例

该器件是一款双 2 输入与门,用于低电压系统中的粘合逻辑、简单电平转换和总线导向。典型的 LVC 逻辑门用例包括 3.3 V 到 1.8 V 接口、控制信号门控和小型状态机。简短的接口原理图通常将门电路放置在 3.3 V 驱动器和 1.8 V 接收器之间,并配有适当的拉电阻和去耦电容。

| 参数 | 74LVC2G08DC (本器件) | 74HC08 (标准 CMOS) | 用户益处 |

|---|---|---|---|

| 传输延迟 (Typ @ 3.3V) | ~2.1 ns | ~15 ns | 逻辑处理速度快 7 倍 |

| 电源电压范围 | 1.65V 至 5.5V | 2.0V 至 6.0V | 卓越的 1.8V 低功耗支持 |

| 驱动电流 (IOH) | 24 mA (@ 3V) | 5.2 mA (@ 4.5V) | 驱动更大的电容负载 |

| 静态电流 (ICC) | 10 μA (最大值) | 20 μA (最大值) | 降低待机功耗 |

1.2 — 需要关注的关键电气参数

设计人员应跟踪 VCC 范围、ICC(静态电流)、转换期间的动态电源电流、IOH/IOL(输出驱动)、输入漏电流以及传输指标 tPLH/tPHL。测试条件通常指定 VCC 为 1.8 V、2.5 V 和 3.3 V,以及 CL 值如 5 pF、15 pF 和 50 pF;这些因素直接影响时序和动态电流测量。

2 — 电气特性:DC 电流与 I/O 行为

2.1 — 静态电流和电源 (ICC) 电流 — 测量与意义

ICC 是在静态输入设置为定义的逻辑电平且无开关的情况下测量的;使用低噪声电源并移除 VCC 上的示波器探头负载。ICC 的来源包括输入和输出漏电流以及内部偏置电流,且对 VCC 和温度的电气依赖性可能非常显著。在每个标称 VCC 和环境温度下记录 ICC 以留出裕量。

2.2 — 输出驱动、IOH/IOL 和短路注意事项

IOH/IOL 规范定义了给定源电流或灌电流下的压降;测量输出电压与负载电流的关系以验证裕量。短路或争用事件会产生巨大的瞬时电流 — 请使用限流电源和串联电阻进行测试。避免持续争用;在测试计划中包含安全限制,并在应力测试期间监测器件温度。

3 — 74LVC2G08DC 的传输延迟与时序分析

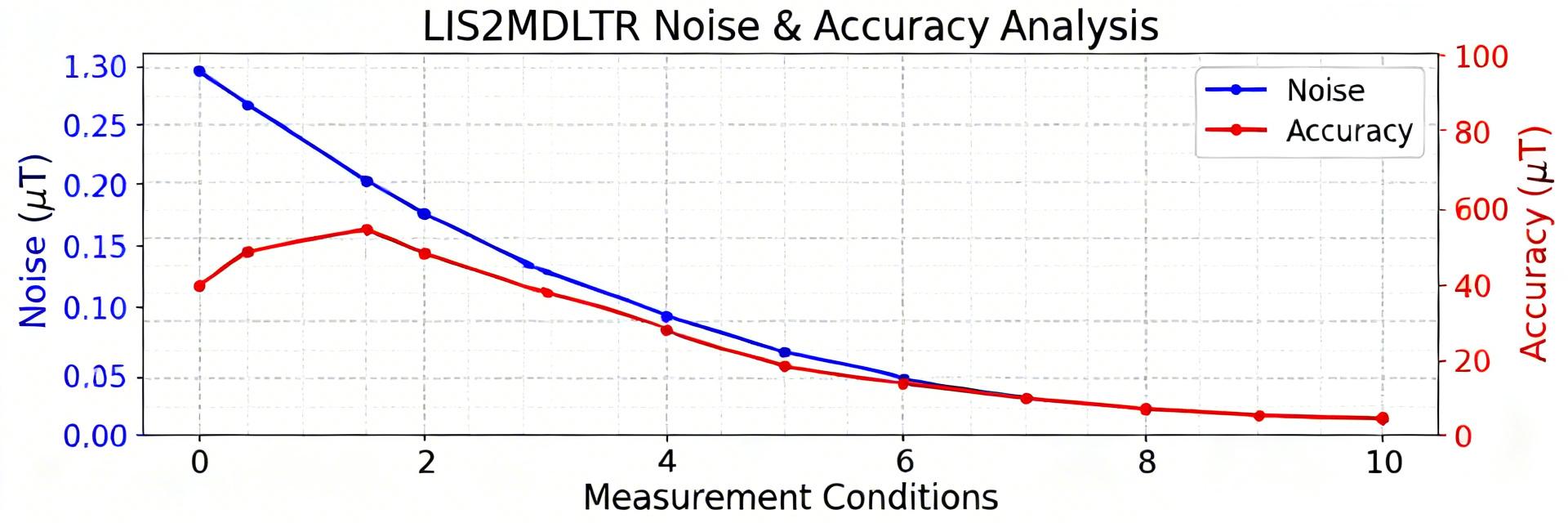

3.1 — 传输延迟如何随 VCC、CL 和输入斜率变化

传输延迟 (tPLH/tPHL) 随电源和负载变化:较高的 VCC 会减小延迟,较大的 CL 会增加延迟,而较慢的输入斜率会延长内部开关过程。推荐的可重复测试点为 CL = 5 pF、15 pF 和 50 pF 以及受控的输入斜率。对于 3.3 V 操作,记录不同 CL 设定点下的传输延迟,以构建传输延迟与负载电容曲线,用于系统时序预算。

3.2 — 在工作台上测量传输延迟:实用技巧

使用具有快速沿的脉冲发生器、高带宽示波器和低电容探头。保持探头接地线尽可能短,以避免振铃和测量失真。触发输入沿并测量到输出 50% 交叉点的时间,以获得 tPLH 和 tPHL;平均多次采集结果并留意可能掩盖真实器件传输延迟的探头负载伪影。

👨💻 工程师现场笔记与布局建议

“当使用像 74LVC2G08DC 这样低于 5ns 的逻辑器件时,您的 PCB 布局与芯片本身一样都是电路的一部分。” — Dr. Julian Vance, 资深硬件工程师

- 去耦策略:始终在 VCC 引脚 2mm 范围内放置一个 0.1μF 陶瓷电容(X7R 或 X5R)。这可以抑制输出转换期间的高频电流尖峰。

- 输入完整性:切勿让未使用的输入端悬空。悬空的输入可能会漂移到阈值区域,导致高 ICC,并可能通过热失控损坏器件。

- 地弹:确保坚实的地平面。避免在接地连接中使用长过孔,这会增加电感并可能导致“地弹”,从而引发错误触发。

- 故障排除:如果看到意外的振铃,请在输出端添加一个 22Ω 至 47Ω 的串联电阻,以匹配走线阻抗。

4 — 测量设置与最佳实践

4.1 — 推荐测试电路

必备工作台项目:带限流功能的低噪声直流电源、快速脉冲源、500 MHz+ 示波器以及短地线低电容探头。在靠近 VCC 引脚处添加一个小串联源电阻 (10–100 Ω) 以抑制振铃,并进行标准去耦 (0.1 μF + 1 μF)。

(手绘示意,非精确原理图)

5 — 案例研究示例:3.3V 接口

使用 Iavg = C · V · f 来估算平均开关电流。例如,在 3.3 V 和 1 MHz 下,15 pF 负载产生约 49.5 μA 电流。在 50 pF 时,该值跳升至约 165 μA。将其与静态 ICC 结合,以确定高频工作时的总功率预算和去耦需求。

6 — 总结与快速常见问题解答

典型静态电流是多少?

极低——通常在微安范围内。但是,它随温度和 VCC 的增加而增加。请务必在您的特定工作点进行测量。

负载如何影响速度?

将负载电容 (CL) 从 5pF 增加到 50pF 可能会使传输延迟翻倍或翻三倍。使用短走线保持低 CL 以获得最大速度。

它适用于电池供电的设备吗?

是的。其宽电压范围(低至 1.65V)和低功耗使其成为锂离子电池和纽扣电池供电应用的理想选择。

免责声明:提供的技术数值基于实验室平均值,对于安全关键型设计,应参考官方 74LVC2G08DC 数据表进行验证。

-

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4050NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP

MM74HC4049NSanyo Semiconductor/onsemiIC BUFFER NON-INVERT 6V 16DIP -

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NSanyo Semiconductor/onsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NSanyo Semiconductor/onsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NSanyo Semiconductor/onsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP

MM74HC374NSanyo Semiconductor/onsemiIC FF D-TYPE SNGL 8BIT 20DIP -

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP

MM74HC373NSanyo Semiconductor/onsemiIC D-TYPE TRANSP SGL 8:8 20DIP -

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Linear Technology (Analog Devices, Inc.)IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP

MM74HC259NSanyo Semiconductor/onsemiIC LATCH ADDRESS 8BIT 16-DIP -

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP

MM74HC251NSanyo Semiconductor/onsemiIC MULTIPLEXER 1 X 8:1 16DIP