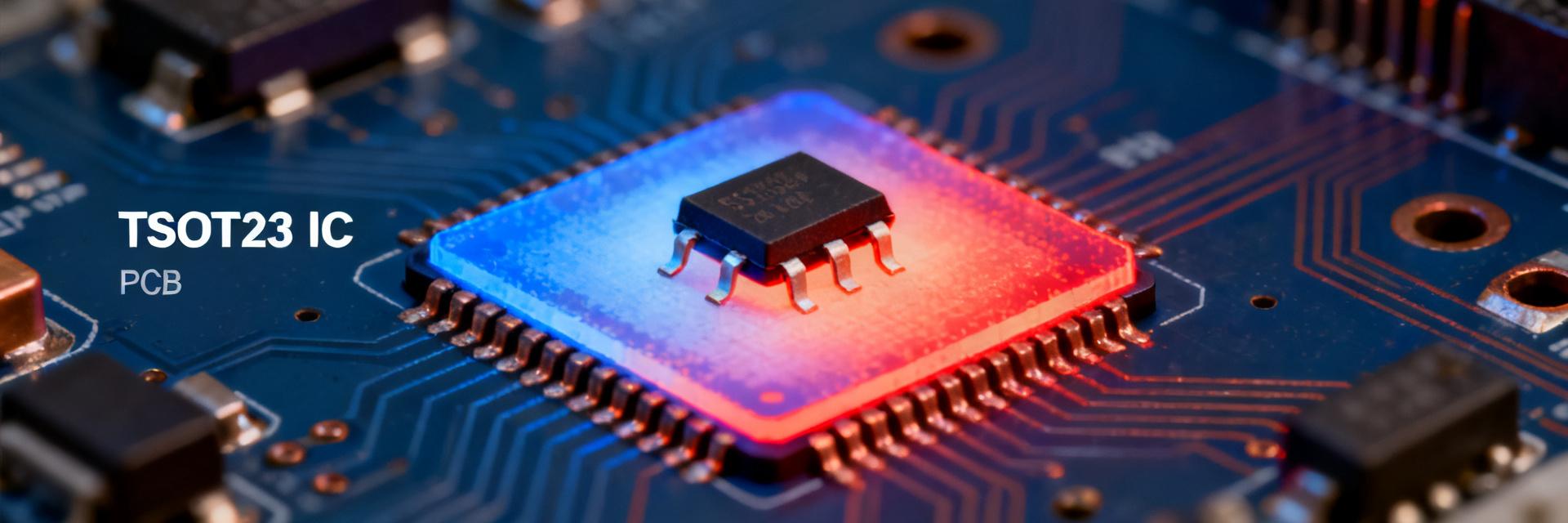

在受控实验室运行中,该器件在广泛的 VIN/VOUT 扫描中表现出明显的中等负载效率峰值;针对多种 PCB 布局重复进行了测量,以量化热灵敏度。测试条件涵盖了从 0.8 V 到 5.0 V 的输出以及从 10 mA 到 2 A 的负载,效率测量不确定度通常为 ±0.3%,板卡热测量不确定度为 ±1.0 °C。 这里的重点是可复现的效率数据和热性能发现,以及在集成到最终产品过程中为保持转换效率和限制温升而采取的具体布局和组件措施。 1 为什么测量效率和热性能很重要(背景) 驱动实测效率的关键电气规格 要点:VIN 范围、VOUT 设定值、开关频率和集成 MOSFET 的 RDS(on) 主导转换损耗。 证据:较低的 VIN 到 VOUT 压差可降低开关应力和传导损耗;较高的开关频率在允许更小无源器件的同时会增加开关损耗。 解释:在展示效率数据之前,重点介绍数据手册参数——VIN 最小/最大值、RDS(on)、静态电流和推荐开关频率,以便读者将观察到的曲线与器件物理特性和电路板选择联系起来。 热性能对可靠性的影响 要点:温升会缩短组件寿命,并可能触发输出漂移或热关断。 证据:结到环境热阻 (θJA) 和结到外壳热阻 (θJC) 决定了给定实测板卡温度下的稳态结温 Tj。 解释:设计人员应监测诸如 VOUT 逐渐偏移、高负载下反复打嗝或热保护激活等症状;包括热裕量计算 (Tj = Tambient + θJA × Pdissipation),并针对持续负载计划降额使用。 2 — 实测效率:测试矩阵和结果(数据分析) 测试矩阵和测量条件 要点:简明的测试矩阵可提高可重复性。证据:测试使用 VIN = 3.3 V 和 5.0 V,VOUT 设定值为 0.8 V、1.2 V、3.3 V,负载点为 10 mA、100 mA、500 mA、1 A 和 2 A,在 23 ±1 °C 的环境温度下以 1 MHz 开关频率运行。解释:报告输入源稳定性、输入功率测量位置(电源处)、检流电阻放置、仪表平均值以及设备型号或精度。 参数 值 VIN 3.3 V, 5.0 V VOUT 0.8 V, 1.2 V, 3.3 V 负载点 10 mA, 100 mA, 500 mA, 1 A, 2 A 开关频率 1 MHz 环境温度 23 ±1 °C, 静止空气 效率结果和解读 要点:效率曲线显示出中等负载峰值,而在轻载和重载两端效率有所降低。证据:当 VIN = 5.0 V 时,1.2 V 输出的实测峰值效率在中等负载下达到 90% 以上;在 100 mA 时,效率比峰值下降约 3-6%,而在 2 A 时,根据布局不同下降约 1-3%。解释:使用效率随负载变化的图表以及不同布局间的效率差值图表来量化布局影响;包含不确定度范围,并指出与同步整流相关的轻载行为。 3 — 热性能:实测温升和热点 案例研究 A:紧凑布局 TSOT23-8 封装,极少铺铜。在 2 A 负载下比环境温度升高 约 25 °C。 案例研究 B:扩展布局 带多个散热过孔的扩展铜平面。在 2 A 负载下温升限制在 约 5–8 °C。 热成像、结温估算和解读 要点:热成像图可识别热点和稳态板卡温度。证据:在每个负载的稳态下捕捉红外帧,并标注最热组件;通过应用 θJA 与实测板卡温度来估算结温 Tj (Tj ≈ Tboard + Pdiss × θJC)。解释:使用热成像来验证手动计算,并在估算的 Tj 接近安全限值时定义限制/降额阈值。 4 — 如何复现测量(方法指南) 所需设备 可编程直流电源(稳定) 电子负载(恒流/动态模式) 校准过的万用表和热像仪 用于开关节点的示波器 测试 PCB:2–4 层,1 盎司铜 测量程序 序列:在标称 VIN 下预热器件 10 分钟,然后扫描负载,每个点允许 60-120 秒稳定。在源端和负载端测量功率,取多个样本的平均值,并捕捉开关波形以确认工作模式。避免长仪表引线,并连续记录环境/板卡温度。 5 — 设计建议(行动指南) PCB 与组件优化 见解:布局更改可产生可衡量的收益。增加铺铜并缩短高电流走线使板卡 ΔT 降低了 10 °C 以上,并将峰值效率提高了约 0.5%。选择具有低 DCR 的电感器,并优先考虑紧凑的高电流回路几何结构。 产品集成清单 ✓ 预期工作负载范围和功耗 (Pdiss) ✓ 热裕量目标 (Tj > 10 °C) ✓ 连续运行的降额规则 ✓ 最终原位效率验证 总结 BD9A201FP4-LBZTL 在中等负载下显示出峰值效率;报告效率数据时应说明不确定度和测试条件。 热性能在很大程度上取决于 PCB 铺铜面积;扩展铺铜和过孔将板卡温升降低了两位数。 可重复的测量需要明确的设备和稳态时序;在集成过程中请使用提供的清单。 常见问题 应如何测试 BD9A201FP4-LBZTL 的轻载效率? 在定义的低电流点(如 10 mA 和 100 mA)进行测量,允许较长的稳定时间以捕捉诸如跳脉冲等模式,并报告平均值和瞬时值;包含测量不确定度并记录示波器观察到的开关行为。 集成到紧凑型产品时建议预留多少热裕量? 目标是使最坏情况下的估算结温与器件的额定连续运行结温限制之间至少保持 10 °C 的裕量;如果裕量不足,请增加铺铜、添加过孔或提供气流散热。 哪些验证步骤可以确认生产就绪? 在最坏情况下的 VIN 和负载下对最终组件运行原位测试,记录效率曲线和热图,验证开关波形,并执行短时间压力测试以验证热稳态及是否存在反复的热关断。 BD9A201FP4-LBZTL 技术文档 | 效率与热性能分析