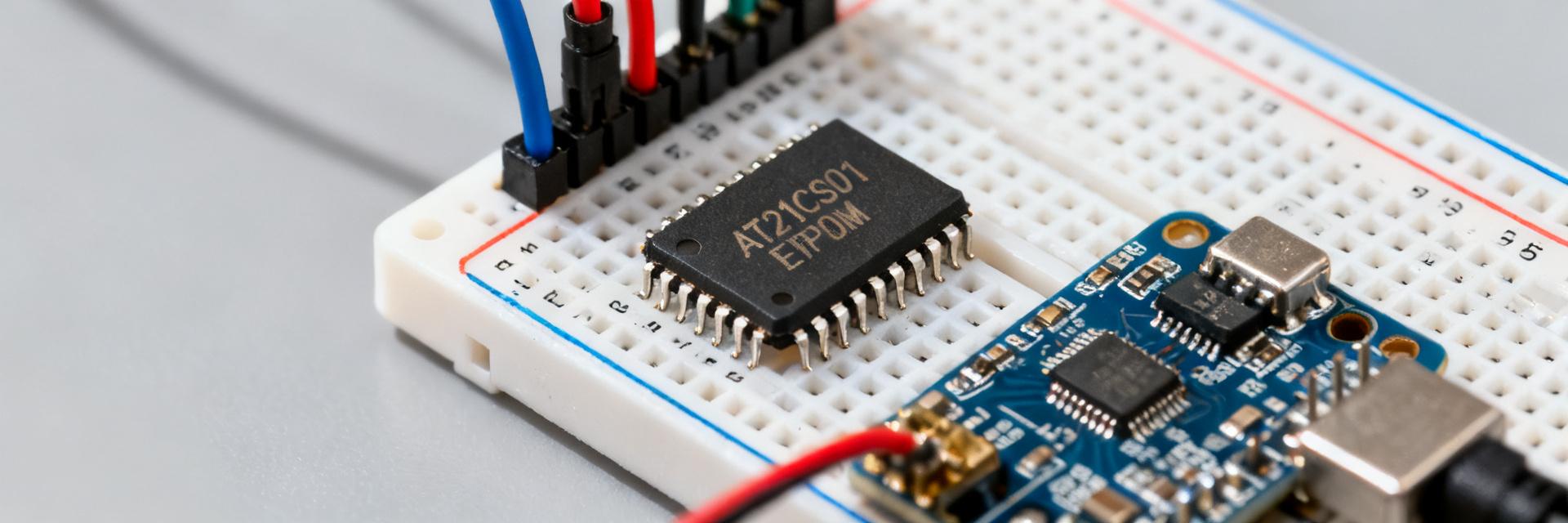

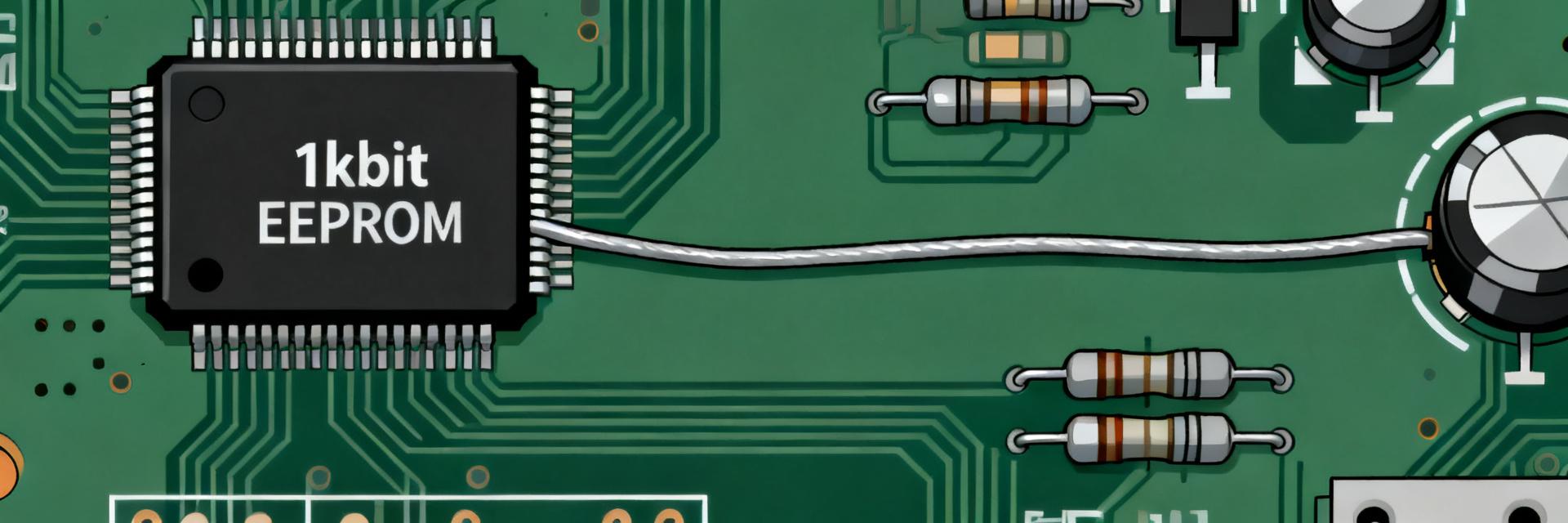

The AT21CS01-MCHM10-T is a compact 1kbit EEPROM with a single‑wire serial interface and a 1.7–3.6 V self‑powered pull‑up input, specifications that directly address ultra‑low pin‑count ID, configuration, and calibration storage in constrained embedded systems. Key datasheet figures—voltage envelope, timing windows, and endurance—drive integration decisions for reliable deployments. This article delivers a compact, testable breakdown of full specs, expected performance, and practical integration guidance based on datasheet figures and common bench tests, enabling engineers to move from paper to validation quickly and with measurable pass/fail criteria. 1 — Product overview & quick specs (background) What the AT21CS01-MCHM10-T is (what to cover) Point: The device is a 1kbit (128 × 8) serial EEPROM implemented as a single‑wire memory/ID device used for serial numbers, small configuration stores, or one‑time calibration values. Evidence: compact density and single‑line protocol reduce BOM and IO. Explanation: designers choose it where minimal pin count and nonvolatile small storage outweigh capacity needs. Quick specs snapshot (what to include) Point: Top‑line electrical and reliability specs guide selection. Evidence: supply/pull‑up 1.7–3.6 V, typical industrial temperature −40 °C to +85 °C, stated data retention and write endurance in the datasheet. Explanation: confirm these fields—density, interface, voltage, temperature, package, write cycles, retention—against target application requirements before prototype. Visual Performance Dashboard Voltage Range 1.7V - 3.6V Capacity 1 Kbit Interface Single-Wire Reliability (Write Endurance) 1,000,000 Cycles (Datasheet Standard) 2 — Electrical characteristics & timing (data analysis) Voltage, current and power considerations (what to analyze) Point: Single‑wire self‑powered operation means the line must provide a reliable pull‑up while the part may source/sink small currents. Evidence: datasheet lists pull‑up input behavior and absolute voltage limits. Explanation: start testing with a ~10 kΩ pull‑up, verify that idle leakage and active-source current meet system budgets, and measure standby vs active currents under real board conditions. Read/write timing and endurance (what to analyze) Point: Timing windows and write procedures determine responsiveness and reliability. Evidence: the datasheet specifies bit timing, read latency, and recommended write‑cycle sequence plus endurance/retention claims. Explanation: implement recommended write delays and acknowledge polling sequences; treat endurance figures as design targets and include write‑cycle budgeting in lifetime estimates. 3 — Environmental, reliability & packaging impact (data analysis) Temperature, retention & ageing (what to analyze) Point: Operating temperature directly affects access times and long‑term retention. Evidence: datasheet gives retention at specified temperatures and may specify accelerated test equivalence. Explanation: validate access time across the planned temperature range and include an accelerated high‑temperature bake to surface potential drift or bit failures before fielding. Mechanical & packaging considerations (what to include) Point: The 2‑lead VSFN footprint reduces board area but increases solder/reflow sensitivity. Evidence: package mechanical data and reflow temperature guidelines appear in the datasheet. Explanation: follow recommended land pattern, control solder fillet and placement, and observe handling/moisture sensitivity precautions to avoid latent solder or delamination failures. 4 — Integration & interface guide (methods) Wiring, pull‑up and signal integrity (what to instruct) Point: Robust wiring and decoupling are essential for stable single‑wire operation. Evidence: single‑wire line shares power/pull‑up duties per manufacturer guidance. Explanation: checklist: one data line to device, common ground, decoupling capacitor near local supply, place pull‑up close to controller, and avoid large trace capacitance—use series resistor if ringing appears on long runs. Command sequence & firmware patterns (what to instruct) Point: A deterministic command flow and error handling keep operations repeatable. Evidence: datasheet lists basic command/transaction structure. Explanation: implement sequence: apply pull‑up, send command byte, address, data, then end condition; use timeouts and limited retries for write operations, log ACK/NAK states and validate readback immediately after write for verification. 5 — Performance testing & benchmarking (methods) Recommended bench tests & metrics (what to run) Point: Targeted bench tests reveal real‑world behavior. Evidence: compare measured latencies and currents to datasheet typicals. Explanation: run read/write latency, write‑cycle verification, retention spot‑checks, idle/active power consumption, and ESD/robustness checks. Use a logic analyzer on the data line and a precision current meter measuring pull‑up node for best insight. Interpreting datasheet vs real‑world results (what to report) Point: Bench results often diverge from datasheet typicals due to fixture and environment. Evidence: timing shifts or higher leakage are common when trace capacitance or board leakage increases. Explanation: document environment, temperature, fixture capacitance, and cable length; apply pass/fail thresholds tied to system needs and iterate pull‑up and timing adjustments when results deviate. 6 — Typical applications & selection checklist (case + action) Common use cases (what to illustrate) Point: Small nonvolatile stores serve multiple common roles. Evidence: 1kbit capacity suits device ID, configuration blobs, or small calibration tables. Explanation: examples: device serial number storage (one‑time writes), sensor calibration constants (occasional updates), and production trace tags; choose this form factor where minimal size and single‑line simplicity matter most. Buy/install checklist & risk assessment (actionable checklist) Point: A pre‑commit checklist reduces integration surprises. Evidence: common failure modes stem from voltage mismatch, footprint errors, or insufficient testing. Explanation: confirm voltage compatibility, verify footprint and reflow profile, run the bench tests listed earlier, budget write cycles for intended usage, and validate alternative device pinout before substitution. Summary The AT21CS01-MCHM10-T delivers compact, single‑wire 1kbit EEPROM storage suitable for low‑pin ID and configuration tasks; verify voltage and pull‑up requirements against system constraints before prototype. Bench tests should include read/write latency, current consumption, and retention spot‑checks; use logic analyzers and high‑precision current meters to reconcile datasheet figures with measured results. Packaging and thermal handling matter: follow recommended footprint, reflow guidance, and moisture handling to minimize assembly and long‑term reliability risks. Action: consult the official datasheet for absolute limits, perform the recommended bench tests, and run the checklist prior to deployment to ensure the device meets system lifetime and environmental requirements. 7 — Frequently Asked Questions What currents should be expected during idle and active states? Idle current is typically very low; active source/sink events occur during bit transitions and write cycles. Measure at the pull‑up to capture combined source/sink behavior, and compare the recorded idle and active currents to datasheet typicals while noting test temperature and pull‑up value for reproducibility. How many write cycles can be expected for field use? Datasheet endurance figures provide a design baseline; use those numbers to estimate lifetime writes. In practice, write‑cycle budgeting in firmware and limiting unnecessary updates protects longevity—perform write‑cycle verification tests to confirm devices meet endurance needs under the expected thermal and mechanical conditions. What are the best first tests when a new PCB includes this device? Begin with a power/pull‑up sanity check, read device ID or blank value, perform a verified write/read sequence, then measure idle and active currents. Log environmental conditions and fixture wiring so results are comparable across prototypes and iterations.